# ANALYSIS, DESIGN & IMPLEMENTATION OF LOW POWER 10T FULL ADDER CIRCUIT

Vijay Kumar Sharma<sup>1</sup>, Prof. Suresh Gawande<sup>2</sup>

<sup>1</sup> M.Tech Scholar, Electronics Engineering Department, Bhabha University, M.P., India <sup>2</sup> Assistant Professor, Electronics Engineering Department, Bhabha University, M.P., India

## ABSTRACT

Full adder is the heart of any central processing unit that is a core component employed in all the processors. This paper presents a design methodology for full adder circuit with minimum number of transistor i.e. reduced size & reduced area. This is then used to implement 10T full adder design for carrying out summation of bits. The analysis of the developed full adder design is done at room temperature CMOS 90 nm and 180 nm technologies using Micro wind tool 2.6. The result shows the comparison between different CMOS technologies in 90 nm and 180 nm using micro wind tool 2.6 on the design in regards of power dissipation, propagation delay and power delay product. A comparison table shown having power, delay and transistor count based comparison at 90 nm and 180 nm technologies showing delay in time and dissipated Power within the full adder summation circuit design at room temperatures. We will also provide the layout of the full adder design at both technologies. The proposed technique shows 96.66% less power consumption in 90 nm and 93.93% less power consumption in 180nm as compare to base paper hybrid logic design.

Keyword :- Full Adder, CMOS, DSCH, MICROWIND, Transmission Gate Logic

#### **1. INTRODUCTION**

Day by day IC technology is obtaining a lot of advanced in terms of style and its performance analysis. A faster speed with lower power consumption and smaller size is implicit to the trendy electronic styles. Full adder usually has extended latency, large space and consumes substantial quantity of power hence low-power full adder style has become a very important part in VLSI system style. Everyday new approaches are being developed to style low-power full adder at technological, physical, circuit and logic levels. Since the full adder is mostly the slowest part during a system, the system's performance is set by performance of the multiplier. Conjointly full adder designs are the foremost space overwhelming entity during a style. Therefore, optimizing speed and space of a full adder may be a major style issue today. However, space and speed are typically conflicting constraints in order that rising speed leads to larger areas and vice-versa. Conjointly space and power consumption of a circuit are linearly related to. Thus a compromise has got to be exhausted speed of the circuit for a bigger improvement in reduction of space and power.

A higher illustration base effectively indicates to fewer digits. Embedded systems style focuses on low Power dissipation and system-on-chip. A reliable on-chip communication customary is a must in any SOC. This section provides an informative review regarding the designing existing mechanism of full adder combinational circuit.

Energy conversion is needed to represent a change in signal value. If energy exists only in one form, i.e. electric energy, then there is only one irreversible energy conversion from electric energy to heat. To break this one-way conversion, researchers have introduced another energy form, i.e. magnetic field energy, into the digital circuit. If one relates the signal change to the conversion of electric energy to magnetic energy the so-called "energy-recovery" can be realized. This is the method by which the irreversible conversion from electric energy to heat caused by dissipative elements, i.e. resistors, is largely reduced or avoided. The energy conversion from electric

field to magnetic field and vice versa implies that circuits should be supplied with AC power. In this case, signals in the circuits should also be alternating quantities. The latter has been extensively used in dynamic CMOS logic, clocked CMOS logic and various domino logics. However, those circuits still rely on DC power, and the energy conversion remains as electric energy to heat. There is need for further study in the case of circuits supplied with AC power. The AC power controls the working rhythm of the circuit and acts as the clock, called the power-clock.

Rest of the paper organize as follows: In the section 2 explain the related work results of various full adder design using different mechanism, problem statement describe in section 3, section 4 describe the proposed design and their mechanism and used simulation tool also, section 5 describe the simulation results of proposed hybrid design, last but not the least discuss the conclusion.

#### 2. RELATED WORK

The analysis [1] introduce that the full adder cells play a significant role in varied VLSI circuits. Therefore, style of associate energy-efficient full adder that operates faithfully in submicron technologies has become a good concern in recent years. Some antecedently designed cells suffer from non-full swing outputs, dynamic consumption and low speed problems. During this paper, 2 high-speed, low-power and full swing full adder circuits are designed in 90-nm CMOS technology. In step with simulation results, the projected circuits have rail to rail output signals. Also, associate improvement of 12%-52%, 7%-48% and 28%-68% has been achieved in delay, power consumption and power-delay product (PDP), severally.

In this paper [2], hybrid logic vogue is adopted to style the total adder. The most objective of this style is to attain Low power and high speed. Hybrid logic vogue used is that the combination of C-CMOS logic (Complementary Metal compound Semiconductor) and Transmission gate (TG) logic. The Circuit was enforced using Micro-wind tool in 90nm and 180nm technology. Performance metrics of power and speed are compared with existing adder styles like typical CMOS adder, Transmission gate adder (TGA) and Transmission operate adder (TFA). Average Power consumption of the projected style is found to be 1.114  $\mu$ W at 90nm for 1.2V offer and 5.641  $\mu$ W at 180nm technologies severally. So overwhelming very low power and needs less time than existing styles for a similar testing setting. Power Delay Product (PDP) is calculated as product of Power and delay values signifies energy demand of the look. Projected style needs 71 less energy than TFA and 81 less energy than TGA and 92 less energy than typical CMOS adder.

The analysis article [3] projected that the planning multipliers that are of high-speed, low power, and regular in layout ar of considerable analysis interest. Speed of the multiplier factor will be magnified by reducing the generated partial merchandise. Several tries are created to cut back the quantity of partial product generated during a multiplication method one in every of them is array multiplier factor. Array multiplier factor 0.5 adders are wont to total the carry products in reduced time. Achieving high speed integrated circuits with low power consumption could be a major concern for the VLSI circuit designers. Most arithmetic operations are done using multiplier factor that is that the major power consuming component within the digital circuits. Primarily the method of multiplication is complete in hardware in terms of shift and adds operation. The optimization of adder has led to the development in performance of multiplier factor. During this paper, a changed full adder using electronic device is projected to attain low power consumption of multiplier factor. To research the potency of projected style, the standard array

multiplier factor structure is employed. The styles are developed using Verilog HDL and therefore the functionalities are verified through simulation using Xilinx. The ASIC synthesis results of the projected multiplier factor shows a mean reduction of 35.45% in power consumption, 40.75% in space, and 15.65% in delay compared to the prevailing approaches.

In trendy applied science and quantum computation [4], reversible logic plays an important role because it has nominal impact on physical entropy. Reversible logic gates have same range of input and output thence power loss because of bit erase operation will be avoided. There are several reversible logic structures which might perform totally different Arithmetic and logic operations as ancient or classical logic structures can do. During this paper, 2 reversible logic structures are projected which might perform operation of addition. These logic structures specifically projected style I and projected style II, generate carry output and carry propagate signal on the idea of 2 reversible logic gates referred to as Fredkin gate and nuclear physicist gate. Performance of projected styles is evaluated in terms of quantum value, constant input, garbage output and delay. It's found that projected style II could be a more sensible choice over projected style I and a few different existing styles.

The Paper [5] mentioned the comparative analysis numerous} Fin-FET based mostly full adder cells designed with various logic designs. The logic designs used for implementation of Fin-FET based mostly 1-bit full adder are Complementary MOS (CMOS), Transmission Gate (TG) and Complementary Pass-Transistor Logic (CPL). The simulations have being done at 10nm, 20nm and 32nm technology node for all full adder cell styles. PTM models for multi-gate transistors (PTM-MG) low power are used for simulations. The performance parameters that were measured analyzed and compared ar average power, leak power, delay, and energy. It's ascertained that less power is consumed in Transmission Gate (TG) primarily based mostly full adder than the Convention full adder and complementary pass-transistor logic (CPL) based full adder in 10nm technology node. Also, found reduction in delay, EDP, and PDP in TG based mostly full adder compared to different cell styles.

The paper [6] terribly large-scale computer circuit (VLSI) style, supported today's CMOS technologies, face numerous challenges. Shrinking junction transistor dimensions, reduction in threshold voltage, and lowering power offer voltage, cause new issues like high leak current, and increase in radiation sensitivity. As an answer for such style challenges, hybrid MTJ/CMOS based mostly style will resolve the difficulty of leak power and produce the advantage of non-volatility. However, radiation-induced soft error remains a problem in such new styles as they have peripheral CMOS elements. As a result, these magnetic-based circuits ar still susceptive to radiation effects. This paper proposes a radiation hardened and low power magnetic full-adder (MFA) for advanced microprocessors. Scrutiny with the previous work, the projected MFA is capable of tolerating any particle. Strike despite the elicited charge. Besides, our MFA circuit offers lower energy consumption in write operation as compared with previous counterparts. They conjointly counsel associate progressive modification to the projected MFA circuit to convey it the advantage of full non-volatility for future nonvolatile microprocessors.

The analysis [7] introduce the answer of the intense drawback of threshold loss that causes non-full-swing at the out-put of 1-bit full adder, an appointment within which all the transistors ar forced to control in sub-threshold regime is projected during this paper. However this may successively bring further space and delay overhead.

During this work, full swing at the output of 1-bit full adder is maintained with reduced space and delay overhead. an extra electrical device operating within the differential voltage mode are substitution the junction transistor that's wont to scale back the brink loss drawback at the output of 9T based mostly full adder as mentioned during this paper. Previous works associated with this domain issues regarding reduction of power of solely 1- bit adder. The work targets power and space reduction of 1/4/8/16 bit adders. Projected adder shows most total powers saving of 46.87 attempts to 25.99 alter reference to 8T and 9T adder configurations severally.

This paper [8] present, a 3 junction transistor XNOR gate. The projected XNOR gate is intended using CADENCE EDA tool and simulates using the SPECTRE VIRTUOSO at 180 nm technology. The projected results are compared with the previous existing styles in term of power and delay. It's ascertained that the ability consumption is reduced by 65.19% for 3 junction transistor XNOR gate and 48.11% for eight junction transistor full adder. It's conjointly ascertained that the delay is reduced by 31.82% for 3 junction transistor XNOR gate and 28.76% for eight junction transistor full adders.

This paper [9] proposes the look of a coffee power, high speed, and energy economical full adder using changed Gate Diffusion Input (GDI) and Mixed Threshold Voltage (MVT) theme in 45nm technology. The projected style on comparison with the normal full adder composed of CMOS transistors, transmission gates and Complementary Pass-Transistor Logic (CPL), severally, exhibited a substantial quantity of reduction in terms of average power consumption (Pang), peak power consumption (Peak), delay time, power delay product (PDP), energy delay product (EDP) in addition as junction transistor count and thence area. Pavg is as low as 7.61x10-7 watt whereas Peak is as low as 6.21x10-5 watt, delay time is found to be 2.05nano second whereas PDP is computed to be as low as 1.56x10-15 Joule and ADP is evaluated to be as low as three.20x10-24 Js for 0.9 V power offer. The simulation of the projected style has been performed in HSPICE and therefore the layout has been designed in Micro-wind.

In this paper [10] they need designed the total Adder using hybrid-CMOS logic vogue by dividing it in 3 modules so it will be optimized at numerous levels. 1st module is associate XOR-XNOR circuit that generates full swing XOR and XNOR outputs at the same time and has a decent driving capability. It conjointly consumes minimum power and provides higher delay performance. Second module could be a total circuit that is additionally a gate and uses carry input and therefore the output of the primary module as input to get total output. Third module could be a carry circuit that uses the output of the primary stage and different inputs to get carry output. Within the new full adder style we've projected new full adder circuit that scale back the ability consumption, delay between due to hold in and PDP by twelve to 100 percent. Simulations are administrated on HSPICE mistreatment TSMC 0.18 µm CMOS technology.

# **3. PROBLEM STATEMENT**

Performance factors such as power, delay, and layout area were evaluated with the existing designs such as complementary pass-transistor logic, transmission gate adder, transmission function adder, hybrid pass-logic with static CMOS output drive full adder. Due to toughness beside CMOS scaling and transistor sizing with the overhead of high input capacitance and requirement of buffers, the adder using this static CMOS. Also this design proves the power dissipation cause due to the stray capacitances and large length interconnects. The circuits design using CMOS logic with large number of transistors and maximum length interconnect tare gradually more existing provider to propagation delay, overall area and power consumption. The main goal of this work is to improve the different function parameters such as power dissipation, path propagation delay and number of transistor used in full adder design compared with the previously existing ones.

## 4. PROPOSED MODULE DESIGN

An energy efficient low power consumption full adder unit has designed with DSCH tool using 10 transistors. The layout of low power consumption energy efficient full adder has create on micro-wind tool at two different nm technology 90 nm, and 180 nm and simulate with using Verilog language which has generated by the DSCH tool. In this proposed work, an energy efficient or low power consumption full adder unit with designed the hybrid logic i.e. combination of complementary metal oxide semiconductor and pass transmission gate logic. Full adder unit performed operation like addition. The layout has made on micro-wind tool for fabrication and power and waveform analysis of design methodology.

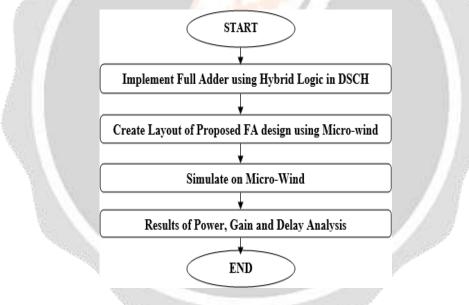

Figure I: Essential Block and Step of Process

Above the figure I depicted that the essential process block and process involves using of simulation and designing software. Here for this architecture design of 10T full adder used DSCH tool for designing and Microwind to obtain power and delay analysis.

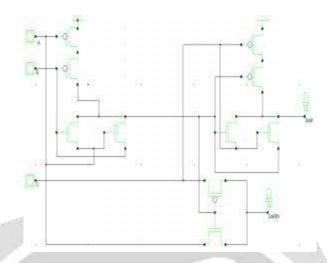

In this thesis, an effort or ways towards the design has been made to design and develop the FA circuit by employing single rail lean i.e. transistor logic method. The advantages of hybrid logic come from the fact that it is best suitable to implement power reduction techniques. By eliminating the glitches we can be reduced switching activity in the circuit. This could be done by the delays of each semiconductor unit dominant the widths and lengths. Switch capacitance of a node at intervals the hybrid logic is progressing to be less as compared to a node at intervals the CMOS design as shown in the figure 2.

Figure II: Architecture Design of Full Adder Circuit using ten transistors

# **5. SIMULATION RESULTS**

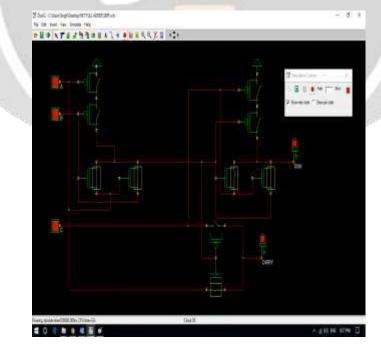

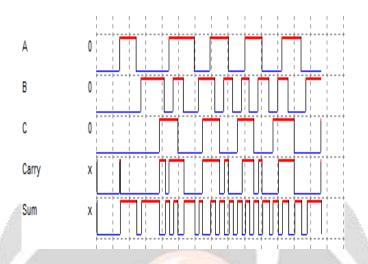

Proposed Full adder with 10T is realized in circuit level with transistor resizing technique as shown in Figure III using DSCH designing software tool 2.7 and timing diagram shown in the figure IV. Layout level of this design is implemented in 90nm and 180nm technology using micro wind tool 2.6 for delay evaluation as shown in figure V and figure VI respectively. Design is carried out in 90nm and 180nm technology to analyze the performance in technology scaling scenarios.

Figure IV: Simulated Overall Timing Diagram of DSCH 10T Full Adder Circuit

Figure V: Layout of 10T Full Adder Circuit Design in Micro-wind (90 nm)

Figure VI: Layout of 10T Full Adder Circuit Design in Micro-wind (180 nm)

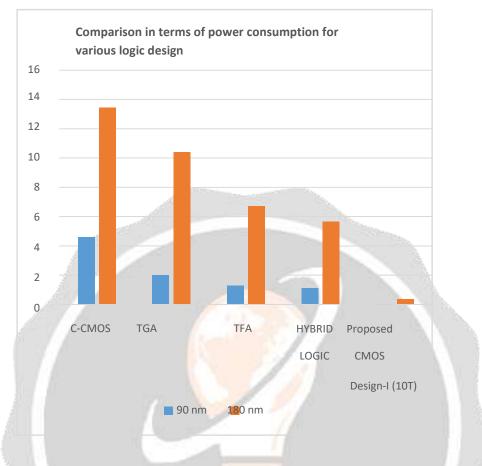

Table I: Comparison between base paper design and proposed design in terms of power consumption for various logic design (1-bit Full Adder)

| LOGIC DESIGN              | 90 nm ( power in<br>μW) | 180 nm( power in<br>μW) |  |

|---------------------------|-------------------------|-------------------------|--|

| C-CMOS                    | 4.609 13.45             |                         |  |

| TGA                       | 1.998                   | 10.42                   |  |

| TFA                       | 1.267                   | 6.709                   |  |

| Hybrid Logic [2]          | 1.114                   | 5.641                   |  |

| Proposed Design<br>(10 T) | 0.037                   | 0.342                   |  |

Figure VII: Comparison between base paper design and proposed design in terms of power consumption for various logic design (1-bit Full Adder)

In the table I and figure VII shows that the average power consumption for various design. In this table we discuss the various designs like C-MOS, TGA, TFA, Hybrid logic and proposed technique and concluded that the proposed design shows less power consumption as compare to base paper design.

| Table II: Comparison of power consumption and improvement as compare to base paper results in |

|-----------------------------------------------------------------------------------------------|

| percentage                                                                                    |

| Power Consumption Value and Improvement in Percentage |           |                                 |                              |  |

|-------------------------------------------------------|-----------|---------------------------------|------------------------------|--|

| Method                                                | Hybrid    | Proposed<br>Design<br>using 10T | Improvement in<br>Percentage |  |

| Technology                                            | Logic [2] |                                 |                              |  |

| 90 nm                                                 | 1.114     | 0.037                           | 96.67 %                      |  |

| 180 nm                                                | 5.641     | 0.342                           | 93.93 %                      |  |

*Summary of Results:* In this paper proposed design consist of ten transistor and using combination of CMOS and transmission gate logic, from discussion or analysis of results concluded as following point.

In the table I and figure VII shows that the average power consumption for various design. In this table we discuss the various designs like C-MOS, TGA, TFA, Hybrid logic and proposed technique and concluded that the proposed design shows 96.66% less power consumption in 90 nm and 93.93% in 180nm less power consumption as compare to base paper design.

## 6. CONCLUSIONS

In this paper proposed design consist of ten transistor and using combination of CMOS and transmission gate logic, from discussion or analysis of results concluded as following point. The average power consumption for various design. In this table we discuss the various designs like C-MOS, TGA, TFA, Hybrid logic and proposed technique and concluded that the proposed design shows 96.66% less power consumption in 90 nm and 93.93% in 180nm less power consumption as compare to base paper design.

## 7. REFERENCES

[1]. Majid AminiValashani and SattarMirzakuchaki, "Two New Energy-Efficient Full Adder designs", 24th Iranian Conference on Electrical Engineering (ICEE) IEEE 2016.

[2]. M Nikhil Theja and Dr T Balakumaran, "Energy Efficient Low Power High Speed Full adder design using Hybrid Logic", International Conference on Circuit, Power and Computing Technologies [ICCPCT] IEEE 2016.

[3]. S. Srikanth and I. ThahiraBanu et al., "Low Power Array Multiplier Using Modified Full Adder", 2nd IEEE International Conference on Engineering and Technology (ICETECH), Coimbatore, TN, India, 17th & 18th March 2016.

[4]. Varun Pratap Singh and manish rai, "Verilog Design of Full Adder Based on Reversible Gates", IEEE 2016.

[5]. Shivani Sharma and Gaurav Soni, "Comparison Analysis of FINFET Based 1-Bit Full Adder Cell Implemented Using Different Logic Styles at 10, 22 and 32nm", IEEE 2016.

[6]. RaminRajaei and SinaBakhtavariMamaghani, "Ultra-Low Power, Highly Reliable, and Nonvolatile Hybrid MTJ/CMOS Based Full- Adder for Future VLSI Design", IEEE Transactions on Device and Materials Reliability 2016.

[7]. SambhuNath Pradhan and Vivek Rai et al., "Design of High Speed and Low Power Full Adder in Subthreshold Region", IEEE 2016.

[8]. Sudhakar Alluri and M.Dasharatha et al., "Design of Low Power High Speed Full Adder Cell with XOR/XNOR Logic Gates", International Conference on Communication and Signal Processing IEEE 2016.

[9]. KrishnenduDhar, "Design of a Low Power, High Speed, Energy Efficient Full Adder Using Modified GDI and MVT Scheme in 45nm Technology", International Conference on Control, Instrumentation, Communication and Computational Technologies (ICCICCT) IEEE 2014.