# A High-Speed in Approximate Reverse Carry Propagate Adder for Energy Efficient DSP Applications

Y.Raja kumari<sup>1</sup>, K.Swaroop<sup>2</sup>

<sup>1</sup>Student, ECE Department, Gandhiji Institute of Science and technology, Andhra Pradesh, India <sup>2</sup>Assistant Professor, ECE Department, Gandhiji Institute of Science and technology, Andhra Pradesh, India

# ABSTRACT

A reverse carry propagate adder is the carry signal that propagates in a counter-flow manner from the most significant bit to the least significant bit. Compared to the output carry signal the input signal has higher significance. This technique for convey engendering prompts higher steadiness within the sight of postpone varieties. Three executions of the invert convey proliferate full-adder (RCPFA) cell with various deferral, power, vitality, and precision levels are presented. The proposed structure might be joined with a precise (forward) convey adder to shape half breed adders with dimensions of exactness. The plan parameters of the proposed RCPA executions and some half and half adders acknowledged using these structures are considered and contrasted and those of the best in class inexact adders utilizing HSPICE re-enactments in a 45-nm CMOS innovation. The outcomes demonstrate that utilizing the proposed RCPAs in the half and half adders may give, by and large, 27%, 6%, and 31% enhancements in postponement, vitality, and vitality delay-item while giving larger amounts of exactness. What's more, the structure is stronger to defer variety contrasted with the customary surmised adder. At long last, the adequacy of the proposed RCPAs is explored in the discrete cosine change (DCT) square of the JPEG pressure and limited drive reaction (FIR) channel applications. The examination uncovers 60% and 39% vitality sparing in the DCT of JPEG and FIR channel, individually, for the proposed RCPAs.

Keyword Reverse Carry Propagate Adder, Adders, Discrete Cosine Change

# 1. Introduction

The power utilization decrease and speed improvement are the key objectives in the structure of computerized handling units, particularly the compact frameworks. Regularly, an expansion in the speed is accomplished at the expense of more power utilization for careful handling units. One of the ways to deal with improve both the power and speed is to forfeit the calculation precision. This methodology, which is surmised processing, might be utilized for the applications where a few blunders might be endured. They incorporate the ones where Digital Signal Processing (DSP) are performed on the human sense-related signs. Since human perceptual capacities are restricted, a large portion of the occasions, the surmised registering might be conjured for custom DSP squares which handling these signs.

Adder blocks, which are the principle segments in number juggling units of DSP frameworks, are control hungry and frequently structure problem area areas on the pass on. These actualities have been the inspirations for understanding this part utilizing the surmised registering approach. Earlier looks into on rough adders have adopted two general strategies of concentrating on blunder weight and mistake likelihood decreases. The primary methodology depends on a mixture structure viper where two unique parts, accurate MSBs, and rough least significant bits (LSBs) are used. The blunder shows up in the convey contribution of the accurate most significant bit (MSB) part and the summation in the LSB part. This constrains the blunder load to the heaviness of the convey contribution of the MSB part. Since regularly the vast majority of the exercises happen in the LSB part, control decreases over 70% might be accomplished utilizing the crossover adder approach. In the second methodology, unadulterated inexact adder structures are utilized. For these adders, decreasing the mistake likelihood of the summation just as diminishing the power and postponement are the key plan criteria. They may likewise be joined by a mistake amendment unit which has time, power, and territory overheads.

We centre around the adders where the utilization of the rough switch Reverse Carry Propagate Full Adder (RCPFA) is proposed. The estimated viper proliferates the information convey in a counter-stream way, i.e., from the higher critical piece to bring down noteworthy piece to frame the convey yield. In this sort of adder, which is called turn around convey Reverse Carry Propagate Adder (RCPA), the proliferation is performed by presenting a conjecture flag going about as a yield flag. Inferable from the turnaround engendering, the heaviness of the convey diminishes as it spreads. This kind of adder improves the deferral and vitality contrasted with those of the cutting edge surmised adders. Additionally, this adder type is less defenceless against the postpone variety when contrasted with the customary ones.

Distinctive acknowledge of the proposed RCPFA are contrasted with those of the cutting-edge inexact FAs. Manages exploring the plan parameters of the proposed FAs and the adequacy of their utilization in a blunder flexible application.

## **II. RELATED WORKS**

A portion of the cutting-edge inexact FAs used in cross breed adders are looked into. The swell conveys Reverse Carry Adder (RCA) has the most minimal power and zone utilization among all the definite carry structures. It, be that as it may, experiences an expansive deferral. To improve the speed and vitality effectiveness of this adder, some earlier works have relinquished the precision. A surmised RCA structure which was called error tolerant adder type I (ETA I) was introduced. In this structure, the information operands are partitioned into careful MS and inaccurate LS parts. In the precise MS part, the customary FAs with a zero convey contribution for the entire part are utilized while the estimated LS part incorporates a convey free expansion part (comprising of XORs) and a control square.

## **III. RESULTS AND DISCUSSION**

The structure parameters of the proposed RCPFAs just as those of the mixture adders acknowledged utilizing these RCPFAs are considered. This paper is performed utilizing the Synopses HSPICE apparatus dependent on a 45-nm NAND Gate innovation. For every one of the recreations, the supply voltage and temperature were 1 V and 25 °C, separately. To have a sense about the innovation parameters, the vitality (delay) of an inverter was reproduced. The effectual of the proposed RCPFAs in two mistake versatile utilization of advanced channel and picture pressure are surveyed.

# A. EXISTING METHOD

There are a portion of the current framework in which the convey flag engenders in a counter stream way from the most noteworthy least piece to the least huge piece. The convey input flag has higher criticalness than the yield convey. This technique for convey proliferation prompts higher security within the sight of defer varieties. Three executions of the switch Reverse Carry Propagate Full Adder (RCPFA) cell with various deferral, power, vitality, and precision levels are presented. The proposed structure might be joined with an accurate (forward) convey adder to shape cross breed adders with dimensions of exactness. The plan parameters of the proposed RCPA executions and some half breed adders acknowledged using these structures are contemplated and contrasted and those of the cutting-edge rough adders utilizing HSPICE reproductions in a 45-nm CMOS innovation. The outcomes demonstrate that utilizing the proposed RCPAs in the cross-breed adders may give, by and large, 27%, 6%, and 31% enhancements in deferral, vitality, and vitality delay-item while giving larger amounts of precision. Furthermore, the structure is stronger to postpone variety contrasted with the customary estimated snake. At last, the viability of the proposed RCPAs is explored in the discrete cosine change (DCT) square of the JPEG pressure and limited drive reaction (FIR) channel applications. The examination uncovers 60% and 39% vitality sparing in the DCT of JPEG and FIR channel, individually, for the proposed RCPAs. The control utilization decrease and speed improvement are the key objectives in the plan of computerized handling units, particularly the compact frameworks. Ordinarily, an expansion in the speed is accomplished at the expense of more power utilization for precise preparing units. One of the ways to deal with improve both the power and speed is to forfeit the calculation precision.

#### **B. PROPOSED METHOD**

In existing framework, since there are numerous disadvantages the turn around conveys proliferate adder is progressively proficient. To structure a rapid territory productive low power low power half and half 64-bit adder for future DSP application. Increment the speed of adder by utilizing low doors and transistor (22n CMOS innovation). Decrease the power utilization by lessening the power supply to 0.8 V. Adder square is the core of ALU, multiplier and processors. Expanding the speed of snake will build the speed of ALU, multiplier and processors. The power utilization decrease and speed improvement can be accomplished. It improves the deferral and vitality. It is less helpless against postponement contrasted with the convectional ones.

The proposed strategy comprises of ease structure. The deferral and blunder can be redressed. To expand the task of DSP. The power utilization decrease and speed improvement can be accomplished. RCPA improves the postponement and vitality than inexact adders. It is less helpless against deferral contrasted with the convectional ones. This outcomes in expanding the speed of the activity of DSP. A large portion of the squares are chosen by ALU and multiplier. Expanding the speed of adder will build the speed of ALU and multiplier. Adder block is the core of ALU and multiplier.

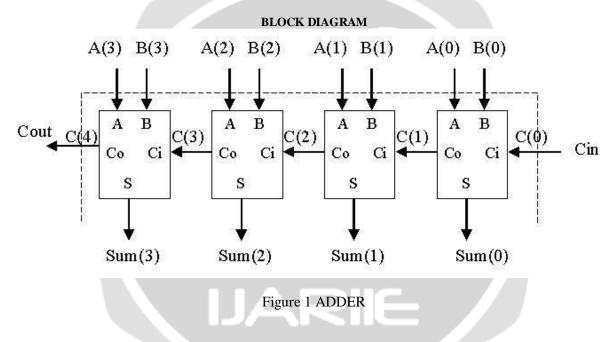

### C. REVERSE CARRY PROPAGATE ADDER

The traditional FA which is the key building square of the convey proliferate adders has three contributions with a similar weight. Also, it has two yields for a summation result with indistinguishable load from that of the sources of info and a convey yield with double the load. The convey proliferation delay (tCP) is the most essential planning parameter in a FA because of the way that it decides the postponement of the basic way of multi-bit adders (and multipliers).

In the most pessimistic scenario, the deferral of the convey engendering snake is  $n \times tCP$  where n is the bit width of the adder. Consequently, a clock period littler than  $n \times tCP$  can result in a setup time infringement and subsequently a potential blunder. A little short-defer infringement may prompt a lot of blunder attributable to the way that the mistake happens on the MSBs of the summation. This is the aftereffect of the age and spread of the help contribution of the MSBs through little noteworthy piece FAs. In view of this thinking, if the request of the convey spread is turned around, one may expect that the measure of mistake because of the planning infringement diminishes. This has motivated us with imagining surmised FAs in which the convey proliferation happens in the switch request (counter-stream course).

# **IV. CONCLUSION**

We proposed estimated RCPFAs which engender convey from most noteworthy to LSBs. The turn around convey proliferation gave higher security in postpone variety. The viability of the proposed surmised FAs and the half and half adders which acknowledged them has been concentrated in 45-nm innovation. The outcomes demonstrated that using the proposed RCPFAs in the half breed adders gives, all things considered, 27%, 6%, and 31% postponement, vitality, and EDP improvement. Furthermore, the proposed RCPFAs were utilized in FIR channel and DCT of the JPEG pressure to assess the exactness and proficiency of the proposed structure in DSP application. The outcomes demonstrated that utilizing the proposed surmised FAs gave by and large 60% and 39% in DCT of the JPEG and FIR channel application separately.

# REFERENCES

[1] O. J. Bedrij, —Carry-select adder, IRE Trans. Electron. Computer, pp340–344,1962.

[2] B. Ramkumar, H.M. Kittur, and P. M. Kannan, —ASIC implementation of modified faster carry save adder, Eur. J. Sci. Res., vol. 42, no. 1, pp.53–58, 2010.

[3] T. Y. Ceiang and M. J. Hsiao, —Carry-select adder using single ripple Carry adder, Electron. Lett, vol. 34, no. 22, pp. 2101–2103, Oct. 1998.

[4] Y. Kim and L.-S. Kim, —64-bit carry-select adder with reduced area, Electron Lett. vol. 37, no. 10, pp. 614–615, May 2001.

[5] J. M. Rabaey, Digtal Integrated Circuits—A Design Perspective.UpperSaddle River, NJ: Prentice-Hall, 2001

[6] Y. He, C. H. Chang, and J. Gu, —An area efficient 64-bit square Root carry-select adder for low power applications, in Proc. IEEE Int. Symp.Circuits Syst., vol. 4, pp. 4082–4085, 2005.

[7] M.D. Ercegovac and T. Lang, —Digital Arithmetic. San Francisco: Morgan Daufmann, ISBN 1-55860-798-6, 2004.

[8] Israel Koren, —Computer Arithmetic Algorithms. Pub A K Peters, ISBN 1-56881-160-8, 2002