# A SIMPLIFIED NESTED NEUTRAL POINT CLAMPED TOPOLOGY FOR MEDIUM VOLTAGE APPLICATIONS

G. Bhavana<sup>1</sup>, M.V. Praveen Reddy<sup>2</sup>

<sup>1</sup> Student, Dept of EEE, Vaageswari college of Engineering, Telangana, India <sup>2</sup> Associate.Prof, Dept of EEE, Vaageswari college of Engineering, Telangana, India

#### ABSTRACT

This paper proposed a nested neutral-point clamped (NNPC) converter of four-level converter topology for medium-voltage applications with interesting properties such as operating over a wide range of voltages (2.4–7.2 KV) without the need for connecting the power semiconductor in series, high quality output voltage, and less number of components in compare to other classical four-level topologies. The control and balance of the flying capacitors (FCs) of the NNPC converter can be done by different control techniques taking advantage of the large number of redundant switching states. This paper presents a simple single-phase modulator for the NNPC converter, which can be applied to each phase of a three-phase NNPC converter. The proposed simple technique can control and balance the FCs to their desired values. Performance of the proposed technique under different operating conditions is investigated in the MATLAB/Simulink environment with R-L load initially and extended with Induction motor load. A solar PV can be fed at the input as DC source for the proposed converter.

Keyword: - Multi-carrier PWM Techniques, Total harmonic distortion, NNPC, FC.

#### 1. INTRODUCTION

Multilevel converters are a very attractive solution for medium-voltage high-power conversion applications; such as motor drives, microgrids, and distributed generation systems. The main features of these topologies, as compared with the two-level voltage-source converters (VSC), are their capabilities to reduce:

- 1) Harmonic distortion of the ac-side waveforms;

- 2) *dv/dt* switching stresses;

- 3) Switching losses; and

- 4) Minimize or even eliminate the interface transformer [1].

Many multilevel topologies have been developed, among them, the neutral-point clamped (NPC), flying capacitor (FC), and the cascaded H-bridge (CHB), are the most studied and well-established multilevel topologies, which are so-called classic multilevel topologies [1]–[5]. Although the classic multilevel converters have been commercialized by major manufacturers, they have some drawbacks, which limit their applications. For instance, an NPC structure with higher number of levels is less attractive and this is because the number of clamping diodes increases substantially with the voltage level. For FC structure, the number of FCs increases with the voltage level. The CHB topology needs a large number of isolated dc sources and an expensive and bulky phase-shifting transformer.

Numbers of variants and new multilevel converters have been proposed in literatures [6]–[15]; however, most of them are variations to the three classic multilevel topologies or hybrids between them, which are so-called advanced multilevel topologies. Among the recent topologies, the following topologies have found practical application, which are commercialized by manufacturers; the five-level H-bridge NPC (5L-HNPC) [6]–[9], the three-level active NPC (3L-ANPC) [10]–[11], the five-level active NPC (5L-ANPC) [12]–[15], and the four-level nested neutral-point clamped (NNPC) converter [16]. A 5L-HNPC is the H-bridge connection of two classic 3L-NPC phase legs, which makes a five-level converter. This topology like an H-bridge topology requires isolated dc sources with the phase-shifting transformer, which increases the cost and complexity of the converter.

A 3L-ANPC is an improved three-level NPC, which can control the loss distribution among the switches of the converter. This topology has higher number of the devices as compared to three-level NPC with the same number of output voltage levels. This increases the cost and complexity of the overall converter. A 5L-ANPC is a combination of a 3L-ANPC and 3L-FC. The main drawback of the 5 L-ANPC converters is that the voltage rating of the switches in one phase of the converter is different.

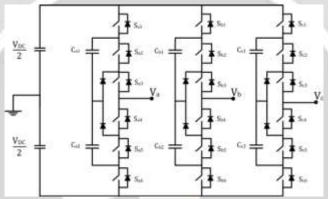

The voltage rate of the outer switches is half of the dc-bus voltage and the voltage rate of the inner switches are 1/4 of the dc-bus voltage. The NNPC converter, as shown in Fig. 1, is a recent multilevel converter topology with interesting properties such as [16]:

- 1) It can operate for a wide range of 2.4–7.2 Kv without device in series;

- 2) It has fewer parts, in compare to same rate previous multilevel converters;

- 3) All the switches have the same voltage stress and equal to one third of the input voltage;

- 4) It does not need any complex transformer;

- 5) The NNPC converter mitigates some drawbacks of the existing topologies, however still the voltage rate that this converter can operate without connecting power semiconductor devices in series is limited to 7.2 kV.

Fig-1: Proposed NNPC converter.

One of the main common issues for the multilevel converter is to control the capacitor voltages at their nominal values to operate the converter properly. For example, for a diode clamped converter the dc-link capacitor voltages should be balanced at nominal values and for a FC converter the voltages of the FCs should be regulated. Different strategies can be applied to control the voltage of capacitors in multilevel converters. One approach is to use auxiliary converter to perform the voltage balancing, which increases the cost and complexity of the overall converter particularly at high-voltage/power levels [17]–[21].

Various modulation strategies have been developed and studied for multilevel converter topologies [12]–[13]. Since the multilevel converters are intended to be used in high-power applications; there are two major challenges in the selection of modulation strategies; high power quality and minimum switching frequency. One modulation strategy for high-power multilevel converters is space vector modulation (SVM), which offers flexibility in the selection of best switching state among the redundant switching states to enhance the dc-bus voltage utilization and better harmonic performance. The SVM scheme generates all the available switching states, switching sequences, and calculates the duty cycles. Some papers just propose new approaches to generate switching states for multilevel converters and they do not address the control issue of the capacitor voltages such as [12], [13] and [14]. Some papers such as [11], [12], and [15], address the issue of voltage balancing of the capacitors using minimum energy property. In this approach, based on the defined cost function, which tries to minimize the difference between the nominal voltage value and the actual value, the best switching states among the all possible switching states can be selected, and finally, apply to the converter. The SVM strategy can generate redundant switching states, particularly at lower modulation index.

Moreover, depends on the converter topology, there may exist some redundant switching states for each voltage level. Theses redundancies increase the number of calculations in the cost function in order to select the best switching state [5], [16]. By the increase in the number of levels, the computational burden for the real-time implementation will increase and sometimes the real-time system cannot handle this task properly, which deteriorate the performance of the converter.

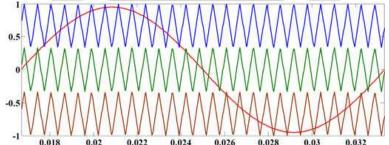

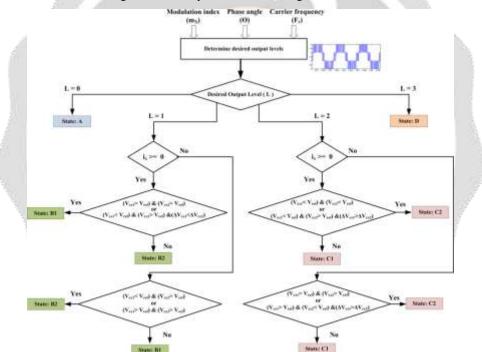

Another modulation scheme that is the most popular modulation scheme in industrial applications is sinusoidal PWM Fig. 2. Block diagram of the proposed SPWM approach for phase *x*.

Fig-2: shows the procedure of the proposed approach.

This modulation scheme is based on the multicarrier PWM strategy. The performance of the different SPWM strategies is studied analytically in [23] to show which SPWM strategy has the better harmonic performance. Moreover, the comprehensive comparison of the SPWM and SVM modulation schemes has been studied in [34]. The main focus of this paper is to propose a new approach using multicarrier SPWM strategy to generate multilevel output voltage, while regulating the voltage of capacitors. This approach employs the deviation of the capacitor voltages from their nominal values and based on the converter output current select the best switching state from the available redundant switching states to charge or discharge the capacitors, and finally, regulate the voltages of capacitors. This approach, unlike the SVM strategy, does not need any cost function and is very intuitive and simple to implement, however, it is very effective.

In this procedure, first, the modulating signal for phase x (x = a,b,c) is compared to carriers (n-1 carriers for an n-level converter), and then, the desired output levels are determined. Based on the desired output level, the corresponding switching state that generates this voltage level can be applied to the power switches. Moreover, there are some redundant switching states for some levels that come from the topology of the converter.

For example, for a four-level FC converter, [32], there are three redundant switching states to generate the two middle levels and for a seven-level topology given in [5], there are more than three redundant switching states for each voltage level. Each redundant switching state is able to charge or discharge the capacitor based on the phase current. If the capacitor voltage is greater than the nominal value ( $\Delta Vxi = Vxi-Vn > 0$ ), the capacitor should be discharged and when the  $\Delta Vxi < 0$  should be charged. Therefore, the appropriate switching state that can charge or discharge the capacitor can be selected and applied to the converter.

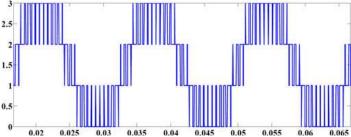

Fig-3: Level-shifted multicarrier modulation for the NNPC inverter.

One of the main advantage of the proposed strategy is that, unlike the SVM strategy, this strategy can be applied for each phase of the converter separately, as a result when the converter is employed to be in different configurations such as the back-to-back structure, cascades H-bridge structure, and modular multilevel structure, the proposed modulation scheme can be implemented easily to generate the output multilevel voltage and also regulate the

capacitor voltages. In this paper, this strategy is developed for an NNPC converter. Fig. 5. Desired output levels based on modulating signal.

0.02 0.025 0.03 0.035 0.04 0.045 0.05 0.055 0.06 Fig-4: Desired output levels based on modulating signal.

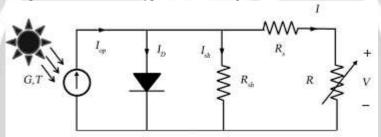

#### 2. EQUIVALENT PHOTOVOLTAIC ARRAY

PV array's output current-voltage curve reflects PV array's dependence on environmental conditions such as ambient temperature and illumination level. Typically, the illumination level ranges from 0 to 1100Wb/m2 and the temperature range is between 233 and 353 K. Normally, we select 1100 and 298 as the reference values for illumination level and temperature respectively. The relationship between PV array's output characteristics and environmental conditions could be illustrated from general simulation results of PV array. PV array's output power is increased as illumination level increases, while PV array's output power is improved with the decrease of the ambient temperature. The equivalent circuit of a typical PV-cell is given below.

Fig-5: Equivalent circuit of photovoltaic cell

Figure reflects a simple equivalent circuit of a photovoltaic cell. The current source which is driven by sunlight is connected with a real diode in parallel. In this case, PV cell presents a p-n junction characteristic of the real diode. The forward current could flow through the diode from p-side to n-side with little loss. However, if the current flows in reverse direction, only little reverse saturation current could get through. All the equations for modelling the PV array are analysed based on this equivalent circuit.

Boost power converters have been widely used for Power Factor Correction (PFC) in AC-DC conversion and for power management in battery powered DC-DC conversions. Moving beyond low-power applications, such as cellular phones, smart phones and other portable electronic products, boost converters are being used more and more in medium-power applications. For example, in computing and consumer electronics, boost converter-based LED drivers for notebook displays, LCD TVs and monitors have been developed. In communications and industrial products, simple boost converters are used in satellite dish auxiliary power supplies and peripheral card supplies. As boost converters run to CCM (Continuous Conduction Mode), a complex pole pair and a Right-Half Plane (RHP) zero will present in the dynamic characteristic. Some applications of boost converter:

- •Programmable soft turn-on for inrush current control

- •Hiccup mode for over-current protection

- •Complete shutdown with source-load separation

- •Simple loop compensation

- •Protection for power MOSFET (Q2) failure

## 3. TOPOLOGY AND OPERATION PRINCIPLE OF THE PROPOSED CONVERTER

A new approach using multicarrier SPWM strategy to generate multilevel output voltage is proposed, while regulating the voltage of capacitors. This approach employs the deviation of the capacitor voltages from their nominal values and based on the converter output current select the best switching state from the available redundant switching states to charge or discharge the capacitors, and finally, regulate the voltages of capacitors. This approach,

unlike the SVM strategy, does not need any cost function and is very intuitive and simple to implement, however, it is very effective. Fig. 1.2 shows the procedure of the proposed approach. In this procedure, first, the modulating signal for phase x (x = a,b,c) is compared to carriers (n-1 carriers for an n-level converter), and then, the desired output levels are obtained.

#### 3. PROPOSED NNPC CONVERTER WITH SVM TECHNIQUE

The NNPC converter is a combination of a FC topology with NPC topology, which provides four level at the output voltage. The capacitor Cx1 and Cx2, x = a, b, c are charged to one third of the total dc-link voltage to ensure equally spaced steps in the output voltages. The NNPC converter in compare to the classic four-level topologies has less number of components and complexity. In compare to a four-level NPC converter, the number of diodes has been reduced from 18 to 6. In compare to a four-level FC converter, the number of FCs has been reduced from 9 to 6. Also, unlike the CHB converter, the NNPC converter does not need to have any isolated dc sources or phase-shifting transformers.

The list of switching combinations is shown in Table I. Four different output levels are achieved from six distinct switching combinations. The NNPC converter can take the advantage of redundancy in switching states to regulate the voltages of the FCs. For generating medium-voltage level 1/6Vdc and -1/6Vdc, there are two redundant switching states. Each redundant state provides a specific charging and discharging current path for each floating capacitor. This is a specific feature of redundant switching states that can be applied to achieve voltage balancing of the FCs. The main technical challenge is to identify the best switching state.

**Fig-6:** Procedure of the proposed SPWM approach for phase x (x = a,b,c).

#### 3.1 SVM Technique for the NNPC Converter

The SVM technique can be applied to the converter to control the output voltage and keep the capacitor voltages balanced and constant [16]. The space vector diagram of a four-level converter on the  $\alpha - \beta$  plane is a hexagon centered at the origin of the plane, as shown in Fig. 6. The reference vector is synthesized by the three adjacent switching vectors and the can be describes as

$$\vec{V}_{1}t_{1} + \vec{V}_{2}t_{2} + \vec{V}_{3}t_{3} = \vec{V}_{ref}T_{s}

t_{1} + t_{2} + t_{3} = T_{s}

\vec{V}_{ref} = |\vec{V}_{ref}| e^{j\theta}, \quad \theta = <\vec{V}_{ref}$$

(1)

$$J = J_a + J_b + J_c$$

$$= \sum_{x} \sum_{i=1}^{2} \frac{1}{2} C_{cxi} \left( V_{C_{exi}} - V_{Dc} / _3 \right)^2$$

$$x = a, b, c. \tag{2}$$

The SVM approach has the following steps to generate three phase output voltages and regulate FCs [16]:

- 1) Identify the sector and triangle where reference vector is located in the  $\alpha$ - $\beta$  coordinate system;

- 2) determine the adjacent switching vectors;

- 3) duty-cycle calculation;

- 4) Determine of redundant switching state combinations

- 5) calculate the average capacitor currents;

- 6) Select the best switching states based on the minimization of energy property of the FCs.

This procedure can produce output voltages and regulate FCs; however, it has lots of calculations, which increases the complexity of the implementation and also introduces a considerable time delay in the actuation. This computational delay can deteriorate the performance of the control system. In order to reduce the complexity of the implementation, and thus, improve the performance of the whole system, a new simple PWM technique presented

#### 3.2 NEW AND SIMPLE SINGLE-PHASE MODULATOR FOR THE NNPC CONVERTER

The proposed single-phase modulator is based on an SPWM technique, which is described in Section I. This technique uses three-level-shifted triangular carriers, all having the same frequency and the same amplitude. The inphase disposition method, where all carriers are in phase, has been employed for the four-level NNPC converter as shown in Fig. 4. Comparing carriers and modulation signal, the desired output levels can be obtained, as shown in Fig. 5. Based on the desired level at the output, the corresponding switching state can be selected from Table I, and then, applied to the power switches. Table I also shows that there are redundancy states for two middle levels (level 1 and 2). The redundancy states based on the direction of the output current can charge or discharge the FCs.

Therefore, after determining the desired output level (by comparing carriers and modulation signal), the direction of the phase current should be measured, and then, the controller will decide which states should be chosen to apply to the converter to control and balance the voltages of capacitors. The selected switching state can charge or discharge the FCs to minimize the difference between the nominal voltage values and the measured voltage values. The diagram shown in Fig. 6 shows the procedure of the proposed SPWM approach. As can be seen from Fig. 5, this procedure is very simple and easy to implement in hardware in compare to the huge amount of calculations for the SVM technique. In the proposed approach, the amount of calculation is independent from the modulation index.

The main feature of the proposed SPWM technique is that it can be applied to each leg separately to control the FCs of that leg and at the same time, generate output waveforms. In different phases, just the modulating signals have  $\pm 120^{\circ}$  phase shift respect to each other.

#### 4. RESULTS AND ANALYSIS

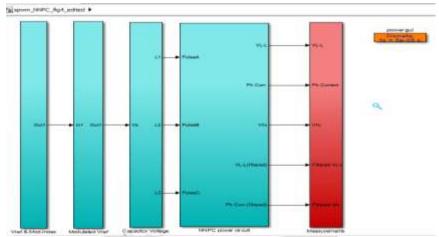

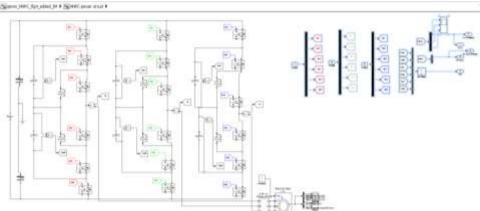

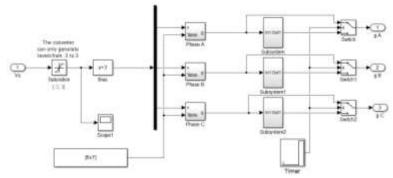

In order to show the performance of the proposed SPWM approach for the NNPC converter, simulation studies have been done in MATLAB/Simulink environment. The simulation studies demonstrate the effectiveness of the developed SPWM to generate output voltages and regulate the voltage of FCs. The parameters used in simulation studies can be found. The performance of the proposed SPWM controller has been studied during steady state and transient state.

Fig-7: Block diagram of proposed system in MATLAB software

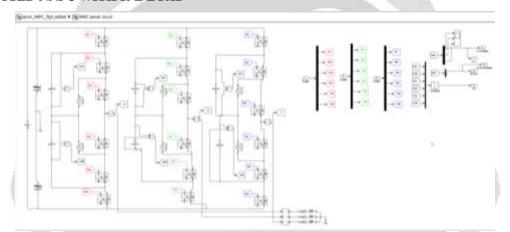

# 4.1 PROPOSED NNPC WITH R-L LOAD

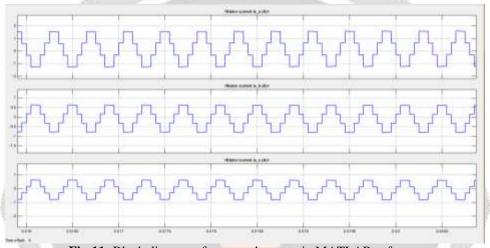

Fig-8: NNPC using proposed control strategy for R-L Load

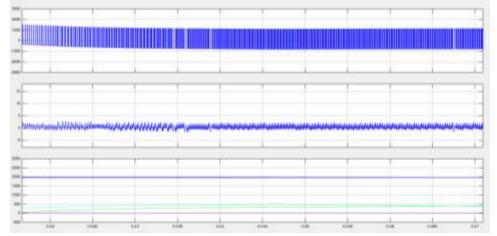

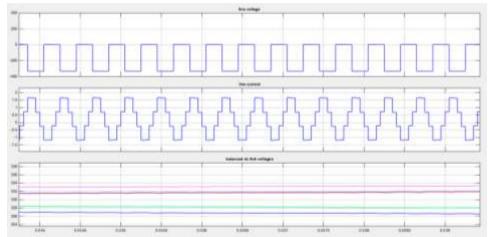

Fig-9: The output phase voltage, line voltage and DC-link voltage of the proposed NNPC

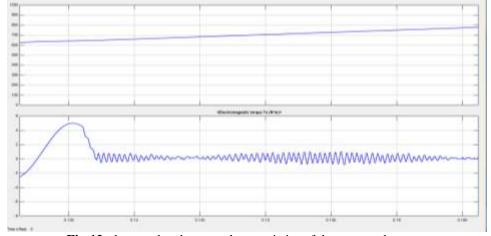

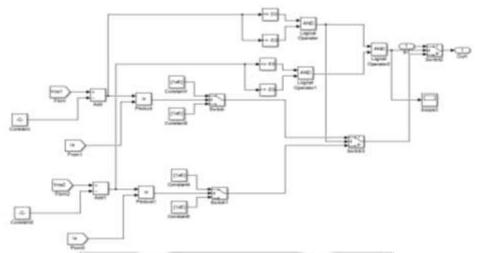

## 4.2 THE PROPOSED NNPC WITH INDUCTION MOTOR LOAD

Fig-10: Block diagram of proposed system in MATLAB software

Fig-11: Block diagram of proposed system in MATLAB software

Fig-12: the speed and torque characteristics of the proposed system

Fig-13: The output phase voltage, line voltage and DC-link voltage of the proposed NNPC

Fig-15: determination of sequence

Fig-16: Trigger signal generation using proposed controller

Fig-17: the circuit of balancing algorithm proposed

#### **CONCLUSION**

This thesis introduces a new SPWM technique for an NNPC converter. The NNPC converter that is a four-level converter topology for medium-voltage applications has interesting properties; operating over a wide range of voltages, high quality output voltage, and less number of components in compare to other classical four-level topologies. This paper presents a simple single-phase modulator that can be applied to each phase of a three-phase NNPC converter and for different phases, the modulating signals have±120° phase shift respect to each other. The proposed technique employs the redundant switching states and selects the best switching state based on the direction of the output current to regulate voltage of FCs to their desired values. Performance of the proposed technique under different operating conditions was investigated in the MATLAB/Simulink environment. The MATLAB simulink design has initially tested with R-L load and then as a part of extension then it is connected to Induction motor of specified range.

#### **REFERENCES**

- [1] S. Kouro, M. Malinowski, K. Gopakumar, J. Pou, L. G. Franquelo, B.Wu, J. Rodriguez, M. A. Perez, and J. I. Leon, "Recent advances and industrial applications of multilevel converters," *IEEE Trans. Ind. Electron.*, vol. 57, no. 8, pp. 2553–2580, Aug. 2010.

- [2] B. Wu, High-Power Converters and AC Drives. Piscataway, NJ, USA: IEEE Press, 2006.

- [3] J. Rodriguez, J. Lai, and F. Z. Peng, "Multilevel inverters: A survey of topologies, controls, and applications," *IEEE Trans. Ind. Electron.*, vol. 49, no. 4, pp. 724–738, Aug. 2002.

- [4] J. Rodriguez, S. Bernet, B. Wu, J. Pontt, and S. Kouro, "Multilevel voltagesource- converter topologies for industrial medium-voltage drives," *IEEE Trans. Ind. Electron.*, vol. 54, no. 6, pp. 2930–2945, Dec. 2007.

- [5] M. Saeedifard, P. M. Barbosa, and P. K. Steimer, "Operation and control of a hybrid seven-level converter," *IEEE Trans. Power Electron.*, vol. 27, no. 2, pp. 652–660, Feb. 2012.

- [6] Z. Cheng and B. Wu, "A novel switching sequence design for five level NPC/H-bridge inverters with improved output voltage spectrum and minimized device switching frequency," *IEEE Trans. Power Electron.*, vol. 22, no. 6, pp. 2138–2145, Nov. 2007.

- [7] I. Etxeberria-Otadui, A. L. de Heredia, J. San-Sebastian, H. Gaztaaga, U. Viscarret, and M. Caballero, "Analysis of a H-NPC topology for an AC traction front-end converter," in *Proc. 13th Power Electron. Motion Control Conf.*, Sep. 1–3, 2008, pp. 1555–1561.

- [8] V. Guennegues, B. Gollentz, L. Leclere, F. Meibody-Tabar, and S. Rael, "Selective harmonic elimination PWM applied to H-bridge topology in high speed applications," in *Proc. Int. Conf. POWERENG*, Mar. 18–20, 2009, pp. 152–156.

- [9] C. M. Wu, W. H. Lau, and H. Chung, "A five-level neutral-point clamped H-bridge PWM inverter with superior harmonics suppression: A NARIMANI *et al.*: NOVEL AND SIMPLE SINGLE-PHASE MODULATOR FOR THE NESTED NEUTRAL-POINT CLAMPED (NNPC) CONVERTER 4077 theoretical analysis," in *Proc. IEEE Int. Symp. Circuits Syst.*, Orlando, FL, USA, May 30–Jun. 2, 1999, vol. 5, pp. 198–201.

- [10] T. Bruckner, S. Bernet, and H. Guldner, "The active NPC converter and its loss-balancing control," *IEEE Trans. Ind. Electron.*, vol. 52, no. 3, pp. 855–868, Jun. 2005.

- [11] O. Apeldoorn, B. Odegard, P. Steimer, and S. Bernet, "A 16 MVA ANPCPEBB with 6 ka IGCTs," in *Proc.Conf. Rec. 40th IEEE IAS Annu. Meeting*, Oct. 2–6, 2005, vol. 2, pp. 818–824.

- [12] J. Meili, S. Ponnaluri, L. Serpa, P. K. Steimer, and J.W. Kolar, "Optimized pulse patterns for the 5-level ANPC converter for high speed high power applications," in *Proc. 32nd IEEE Ind. Electron. Conf.*, Nov. 6–10, 2006, pp. 2587–2592.

- [13] L. A. Serpa, P. M. Barbosa, P. K. Steimer, and J. W. Kolar, "Five level virtual-flux direct power control for the active neutral-point clamped multilevel inverter," in *Proc. IEEE Power Electron. Spec. Conf.*, Jun. 15–19, 2008, pp. 1668–1674.

- [14] F. Kieferndorf, M. Basler, L. A. Serpa, J.-H. Fabian, A. Coccia, and G. A. Scheuer, "A new medium voltage drive system based on anpc-51 technology," in *Proc. IEEE-Int. Conf. Ind. Technol.*, Vi na del Mar, Chile, Mar. 2010, pp. 605–611.

- [15] P. Barbosa, P. Steimer, J. Steinke, L. Meysenc, M. Winkelnkemper, and N. Celanovic, "Active neutral-point-clamped multilevel converters," in *Proc. IEEE 36th Power Electron. Spec. Conf.*, Jun. 16, 2005, pp. 2296–2301.

- [16] M. Narimani, B. Wu, G. Cheng, and N. Zargari, "A New nested neutral point clamped (NNPC) converter for medium-voltage (MV) power conversion," *IEEE Trans. Power Electron.*, vol. 29, no. 12, pp. 6375–5382, Dec. 2014.

- [17] K. Hasegawa and H. Akagi, "A newdc-balancing circuit including a single coupled inductor for a five-level diode-clamped PWM converter," *IEEE Trans. Ind. Appl.*, vol. 47, no. 2, pp. 841–852, Mar./Apr. 2011.

- [18] Z. Pan, F. Z. Peng, K. A. Corzine, V. R. Stefanovic, J. M. Leuthen, and S. Gataric, "Voltage balancing control of diode-clamped multilevelrectifier/inverter systems," *IEEE Trans. Ind. Appl.*, vol. 41, no. 6, pp. 1698–1706, Nov./Dec. 2005.

- [19] E. K. K. Sng, S. S. Choi, and D. M. Vilathgamuwa, "Analysis of series compensation and dc-link voltage controls of a transformerless selfcharging dynamic voltage restorer," *IEEE Trans. Power Del.*, vol. 19, no. 3, pp. 1511–1518, Jul. 2004.

- [20] H. Fujita and H. Akagi, "A practical approach to harmonic compensation in power systems-series connection of passive and active filters," *IEEE Trans. Ind. Appl.*, vol. 27, no. 6, pp. 1020–1025, Nov./Dec. 1991.