# Artificial Intelligence in Integrated Circuit Design: Revolutionizing Productivity Amidst Practical Challenges

Khanh Pham Duy<sup>1\*</sup>

<sup>1</sup>Thai Nguyen University of Technology, Thai Nguyen city, Viet Nam \*Corresponding Author: Khanh Pham Duy

#### **ABSTRACT**

The relentless progression of Moore's Law has pushed the semiconductor industry into an era of unprecedented complexity, where traditional IC design methods are being stretched to their physical and technological limits. Artificial Intelligence (AI) and Machine Learning (ML) have emerged as solutions that promise to revolutionize the EDA design process. By automating complex tasks and exploring large design spaces, AI tools are proving to accelerate design cycles and optimize PPA (Power-Performance-Area) metrics.

This paper provides a comprehensive analysis of current applications of AI across the entire IC design process, from architectural layout planning to final verification. However, the paper also points out the fundamental limitations of AI technology despite its great support for engineers in the IC design process. The paper also points out that the contextual understanding, critical thinking, intuition and experience of IC engineers are still indispensable. Therefore, human intuition and expertise remain the indispensable core of the design process, especially for complex SoCs, analog circuits and mixed-signal circuits. The author will also analyze the practical applications of AI in the modern IC design cycle, and delve into the core limitations that keep humans at the center of the creative and problem-solving process. Therefore, the future lies not in AI replacing engineers, but in a symbiotic relationship that enhances human ingenuity.

**Keyword:** IC design, microelectronics, semiconductor industry, Artificial Intelligence, Machine Learning, Electronic Design Automation (EDA)

#### 1. INTRODUCTION

The design of modern integrated circuits (ICs) is one of the most complex engineering disciplines today. With transistor counts reaching tens of billions on a System on a Chip (SoC) and process nodes shrinking to single-digit nanometer scale, the challenges associated with completing designs, design verification, and shortening time to market have become major issues. The design flow using traditional EDA, while highly sophisticated, often involves time-consuming, iterative processes that are highly dependent on the designer's experience and engineering approach.

In this context, Artificial Intelligence has moved from a theoretical concept to a practical and disruptive technology in the EDA industry. Leading EDA vendors and hyperscalers are implementing AI-driven solutions that leverage techniques such as reinforcement learning (RL) and deep learning (DL) to solve difficult optimization problems. Recent reports show that these AI tools can reduce design iteration times by about 30%, significantly reduce simulation latency, and improve key metrics such as power consumption, performance, and area (PPA). This paper will first survey the most advanced AI applications in the IC design ecosystem, classifying them according to their role in the standard design flow. Subsequently, it will provide a critical analysis of the inherent limitations and blind spots of current AI technologies, highlighting tasks and areas where a keen engineer's judgment is truly needed [1-3],[6], [9-12].

#### 2. POTENTIAL AND APPLICATIONS OF AI IN THE IC DESIGN CYCLE

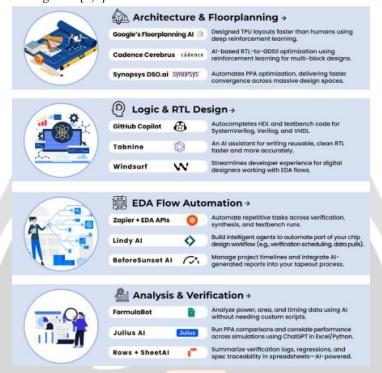

As AI is increasingly integrated into the IC design cycle, many advanced tools such as **Google Floorplanning** AI, Cadence Cerebrus, Synopsys DSO.ai, GitHub Copilot, Lindy AI, etc. have been providing strong support to design teams. Based on the tools being developed, the application of AI can be classified into four main stages of the IC design cycle as shown in Figure 1 [1,7].

Fig -1: Best AI Tools for chip design teams.

#### 2.1 Architecture and Physical Design

This is an area where AI, especially reinforcement learning, has proven to be particularly effective. The most celebrated application of AI in chip design is in physical design, specifically floorplanning and place-and-route (PnR). Pioneering tools such as **Google's Floorplanning AI**, **Cadence Cerebrus**, and **Synopsys DSO.ai** are capable of automatically optimizing the placement of millions of logic blocks (macros) and standard cells. By exploring a huge design space, AI can find optimal PPA floorplan configurations much faster than humans, accelerating convergence [3].

- AI-Driven Floorplanning: EDA tools like Google's Floorplanning AI, which famously designed layouts for its TPU processors faster than human teams, utilize deep reinforcement learning. The AI agent treats the floorplan as a game board, receiving rewards for placements that improve PPA indexes and penalties for those that worsen them. Through thousands of trainings, the agent learns strategies to generate superior floorplans.

- Full-Flow PPA Optimization: Extending this concept, Cadence Cerebrus and Synopsys DSO.ai (Design Space Optimization AI) offer a more holistic, RTL-to-GDSII optimization. These platforms use machine learning to intelligently tune the vast number of parameters and tool settings across the entire synthesis and implementation flow. They can automatically adjust synthesis strategies, placement parameters, and clock tree synthesis options to converge on a PPA target much faster than manual iteration [4,5].

#### 2.2 Logic and RTL Design

In the front-end design phase, AI is primarily emerging as an intelligent assistant to boost developer productivity.

• HDL Code Generation: Tools such as GitHub Copilot and Tabnine are being trained on massive corpora of open-source hardware description language (HDL) code. They provide intelligent autocompletion for

SystemVerilog, Verilog, and VHDL, suggesting entire blocks of code, module instantiations, and testbench structures. This accelerates the coding process and reduces syntactical errors, allowing engineers to focus on higher-level architectural decisions.

• **Testbench Automation:** These assistants can also generate boilerplate for testbenches, including stimulus generation and basic checking mechanisms, which streamlines the initial phases of verification.

#### 2.3 EDA Flow Automation and Project Management

Modern EDA workflows are characterized by a highly complex sequence of iterative processes, such as logic synthesis, formal verification, and parasitic extraction. These workflows necessitate the orchestration of numerous specialized tools, often interconnected through intricate scripting environments. To manage this inherent complexity, the semiconductor industry is increasingly leveraging Artificial Intelligence (AI) to develop intelligent agents for task automation. By interfacing with the Application Programming Interfaces (APIs) of constituent EDA tools, these agents can systematically execute and manage critical design stages, including the scheduling of verification regressions, automated report generation, and real-time project status tracking.

AI is being used to manage complex scripts that connect dozens of tools in modern EDA workflows.

- Intelligent Agents: Platforms like Lindy AI or integrations using Zapier with EDA APIs allow for the creation of intelligent agents. These agents can automate repetitive workflows, such as scheduling and launching verification regressions, parsing results, pulling data from various reports, and populating dashboards.

- Timeline and Tapeout Management: Tools like BeforeSunset AI can help manage project timelines by integrating AI-generated reports into the tapeout process, providing predictive insights into potential schedule slips based on current progress and historical data.

#### 2.4 Analysis and Verification

The verification process generates terabytes of data in the form of logs, waveforms, and reports. AI excels at finding patterns in such vast datasets.

- Log and Report Summarization: Tools like Rows + SheetAI can parse thousands of lines from regression logs or timing reports and summarize key information—such as the number of new failures, trends in timing violations, or spec traceability—directly in a spreadsheet format. This is an AI tool used to replace custom Perl or Python scripts.

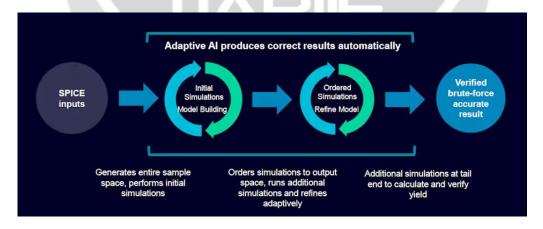

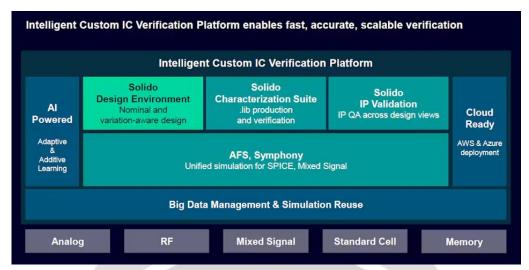

- **PPA Correlation:** Using platforms like **Julius AI**, engineers can run complex queries on performance data using natural language. For example, one could ask to "correlate performance across simulations using ChatGPT in Excel/Python," allowing for rapid PPA comparison between different design iterations without manual data crunching. The use of AI tools in IC design and verification by Siemens is shown in Figure 2 and Figure 3 [8].

Fig -2: Applying "adaptive" AI to custom IC verification of Siemens.

Fig -3: Solido fits into the Siemens IC design and verification suite.

## 3. THE INHERENT LIMITATIONS AND IRREPLACEABLE ROLE OF THE MICROCHIP DESIGN ENGINEER

Although AI tools are proving invaluable to IC design engineers, they currently function as highly specialized optimization engines rather than sentient designers. They possess fundamental limitations that underscore the irreplaceable value of human expertise.

#### 3.1 Limits on Layout Optimization and Design Ideas

While AI is powerful in floorplanning, it struggles to handle complex real-world constraints such as the location of I/O pins, analog pads, ESD protection cells, or decap cells. More importantly, AI does not understand the "design intent" that only human engineers can understand. It cannot make strategic trade-offs on its own, and it cannot ensure that important sign-off factors such as EM/IR drop, congestion, and signal integrity (SI) are met simultaneously and comprehensively.

While an AI agent can optimize a floorplan based on a reward function, it still doesn't understand the reasoning behind the design.

- Complex constraints: AI struggles with abstract and non-quantifiable constraints, such as the strategic placement of I/O pads for a particular package, sensitive routing requirements for analog blocks, or careful distribution of ESD and decap cells.

- Lack of holistic awareness: AI can optimize timing in one corner, but accidentally introduce irreversible IR loss or signal integrity (SI) issues elsewhere. It lacks the holistic, multi-physics understanding that an engineer would have to anticipate and mitigate these cross-domain effects. "Design intent"—the strategic vision of how a chip should function and be physically realized—is a human concept that AI has yet to grasp.

#### 3.2 Gaps in Logical Perception and System Architecture

Als that support RTL are strong in syntax, not semantics. They cannot verify the "logic intent" in complex blocks like finite state machines (FSMs) or Clock Domain Crossing (CDCs). They also cannot write specialized signal processing modules (FIR/IIR, CORDICs) or understand large system architectures like complex pipelines and cross-module interactions.

- No logical intent verification: AI can write syntactically correct code for a Finite State Machine (FSM), but cannot verify that the state transitions correctly implement the intended protocol. AI is particularly weak in areas that require deep logical reasoning, such as designing secure Clock Domain Crossing (CDC) or Reset Domain Crossing (RDC) circuits.

- Inability to create new algorithms: AI cannot design specialized signal processing modules such as FIR/IIR digital filters or CORDIC algorithms on its own. These require deep understanding of mathematical principles and their efficient implementation on hardware, a human area of innovation. AI also lacks system-level architectural awareness to understand complex pipeline interactions or dependencies between modules.

#### 3.3 Challenges in Debugging and Advanced Decision-Making

When EDA flows encounter runtime errors such as DRC/LVS violations, current AI tools cannot debug them on their own. They also cannot differentiate between false and real errors – a skill that requires deep experience on the part of the design engineer. Furthermore, choosing the right tool for each corner-case (e.g., choosing between traditional PEX and EMIR-aware extraction) still requires the engineer's judgment.

Debugging is a process of hypothesising, experimenting, and reasoning. It is very different from pattern matching.

- Runtime error analysis: When a design flow fails with a cryptic runtime error (e.g., a complex DRC or LVS violation), AI cannot debug the root cause. AI cannot interpret the tool's error message in the context of the design and engineering process.

- Distinguishing false errors from true errors: A key part of a senior engineer's job is to ignore false violations—errors that are flagged by the tool and are acceptable in practice. This requires deep judgment based on the designer's experience that AI, which treats all violations as mathematically equal, lacks.

- Choosing the right tool: The engineer knows when to use the traditional PEX (Parasitic Extraction) tool instead of the more computationally expensive EMIR cognitive extraction tool based on the criticality of a particular block. AI lacks this strategic decision-making ability.

#### 3.4 The Inability for Root Cause Analysis and Strategic design Intervention

AI can point to a timing violation or a DRC hotspot, but it cannot determine the root cause: whether it is due to weak drive strength, improper transistor sizing, or crosstalk. Similarly, AI cannot make strategic decisions about changing cell layouts, adjusting metal stacks, or choosing packaging technologies such as chiplets or 3D-ICs. These are decisions that require the integrated knowledge of semiconductor physics, fabrication processes, and system architecture of an IC design engineer.

AI can identify correlations but struggles with causation.

- Deep root cause analysis: AI can flag timing path violations or DRC hotspots. However, it cannot perform root cause analysis to determine whether the problem stems from weak drive strength, an inadequate transistor size, sub-optimal routing, or crosstalk noise from an adjacent buses.

- Choosing the right design strategy: Importantly, AI cannot make strategic decisions involving cross-domain trade-offs. AI cannot decide to redesign a standard cell layout, change the metal stack for better power delivery, or choose a different packaging technology (e.g., chiplet vs. monolithic 3D-IC) based on system-level PPA goals and costs.

### 4. THE HUMAN ROLE REMAINS CENTRAL TO THE IC DESIGN PROCESS, WHICH AI CANNOT REPLACE

Through analyzing some of the limitations of the above AI tools in the field of IC design, we can see clearly that the role of engineers is indispensable, especially in stages that require in-depth experience such as:

- In Digital IC Design: This includes writing timing-critical RTL with careful consideration for clock gating to prevent glitches, architecting complex pipeline structures, defining the strategy for functional simulation and formal verification, and manually guiding the routing of critical paths or high-congestion areas.

- In Analog IC Design: This field remains an art form heavily reliant on human expertise. Transistor-level design of Op-amps, Comparators, and Bandgaps requires an intuitive grasp of noise, mismatch, and layout-aware behaviors. Manual layout techniques like common-centroid and interdigitation, as well as tuning bias currents to compensate for PVT and aging effects, are skills beyond the reach of current AI.

- In Mixed-Signal IC Design: Engineers are essential for designing the critical interface between the analog and digital worlds (ADCs, DACs, PLLs, CDRs). They set up complex AMS co-simulations using SystemVerilog-AMS or Verilog-A and are solely responsible for addressing subtle system-level issues like jitter, latency, and coupling noise in a real-world chip environment.

#### 5. CONCLUSIONS

Artificial intelligence is certainly a technological revolution, acting as a powerful assistant to help IC engineers speed up the IC design process and scale up their work. AI can automate intermediate steps, optimize problems with clear solution spaces, and analyze data at high speed. Besides the advantages of AI tools supporting IC design, it still has inherent limitations that currently only humans can perform. AI cannot replace the core qualities of an excellent

engineer such as intuition, critical thinking, and accumulated experience. In complex systems such as SoC, ASIC, or analog/mixed-signal designs at advanced technology nodes, humans are still the central factor to make decisions, debug, innovate, and ensure the success of a chip. The future of IC design is not "AI replacing humans", but the resonance between the intelligence of engineers and the computing power of AI. The AI-augmented engineer, equipped with intelligent tools, will be the one to design the next generation of world-changing integrated circuits.

#### 6. ACKNOWLEDGEMENT

The author gratefully acknowledge Thai Nguyen University of Technology for supporting this research. (<a href="http://www.tnut.edu.vn">http://www.tnut.edu.vn</a>). This research was not affiliated with any funded scientific project.

#### 7. REFERENCES

- [1]. Report results of Vietnam Semiconductor and Artificial Intelligence Forum.

- [2]. Deepthi Amuru, Harsha V. Vudumula, Pavan K Cherupally, Sushanth R Gurram, Amir Ahmad, Andleeb Zahra and Zia Abbas, AI/ML Algorithms and Applications in VLSI Design and Technology, Computer Science, Machine Learning, Cornell University, arXiv:2202.10015v2, 15 Feb 2023.

- [3]. Matt Graham, Application of AI in IC Design and Verification, Cadence Design Systems, Inc., June 2023.

- [4]. Keren Zhu, Mingjie Liu, Hao Chen, Zheng Zhao, David Z. Pan, Exploring Logic Optimizations with Reinforcement Learning and Graph Convolutional Network, ACM/IEEE Workshop on Machine Learning for CAD (MLCAD '20), November 16–20, 2020, Virtual Event, Iceland.

- [5]. Pingakshya Goswami, Dinesh Bhatia, Application of Machine Learning in FPGA EDA Tool Development, IEEE Access, Volume 11, Page(s): 109564 109580, October 2023.

- [6] Qiguang Chen, Mingda Yang, Libo Qin, Jinhao Liu, Zheng Yan, Jiannan Guan, Dengyun Peng, Yiyan Ji, Hanjing Li, Mengkang Hu, Yimeng Zhang, Yihao Liang, Yuhang Zhou, Jiaqi Wang, Zhi Chen, Wanxiang Che, Al4Research: A Survey of Artificial Intelligence for Scientific Research, Computer Science, Cornell University, arXiv:2507.01903v1, 2 Jul 2025.

- [7]. Nguyen Huong, AISC 2025: Vietnam's new role in AI and semiconductors, The 2025 International Conference on AI and Semiconductors (AISC), 12-14 March, 2025. <a href="https://vir.com.vn/aisc-2025-vietnams-new-role-in-ai-and-semiconductors-124361.html">https://vir.com.vn/aisc-2025-vietnams-new-role-in-ai-and-semiconductors-124361.html</a>

- [8]. https://www.electronicdesign.com/technologies/embedded/article/21272567/electronic-design-ai-lends-a-helping-hand-with-analog-and-custom-ic-design

- [9]. https://phongvu.vn/cong-nghe/ai-thay-ky-su-thiet-ke-hon-50-chip

- [10]. https://www.tessolve.com/blogs/how-do-ai-powered-eda-tools-shape-the-future-of-chip-design

- [11]. IEEE CAS Vietnam Chapter and VNU Information Technology Institute & VNU International School, *The 9th International Conference on Integrated Circuits, Design, and Verification (ICDV 2024)*, June 6-8, 2024. <a href="https://www.is.vnu.edu.vn/nhieu-nghien-cuu-moi-ve-thuat-toan-ai-ung-dung-trong-doi-song-tai-hoi-nghi-quoc-te-ve-thiet-ke-va-kiem-chung-vi-mach-tich-hop">https://www.is.vnu.edu.vn/nhieu-nghien-cuu-moi-ve-thuat-toan-ai-ung-dung-trong-doi-song-tai-hoi-nghi-quoc-te-ve-thiet-ke-va-kiem-chung-vi-mach-tich-hop</a>

- [12]. https://citgroup.vn/ung-dung-ai-trong-thiet-ke-chip.html