# DESIGN AND IMPLEMENTATION OF LOW POWER DYNAMIC LATCH COMPARATOR

Praveen Kumar N.C <sup>1</sup>, Ananth. V. Naik <sup>2</sup>, Bharath Kumar. S<sup>3</sup>, Gayathri K.M <sup>4</sup>

<sup>1</sup>P G Student, <sup>2, 3</sup> UG Students, <sup>4</sup> Assistant Professor,

<sup>1, 2, 3, 4</sup> Department of Electronics and Communication Engineering, School of Engineering and Technology,

Jain University, Bangalore.

In this article we composed a low power comparator for a use of low power simple to advanced converters. In advanced correspondence and sign preparing frameworks, ADC's assume a noteworthy part. To show signs of improvement execution of ADC's we outlined low power utilization comparator. The proposed comparator has a best execution than past best outlines. It is outlined in Cadence 180nm CMOS process and 90nm CMOS process with supply voltages from 0.8V to 1.8V. This outline works with up to clock recurrence of 900MHz and information recurrence of 10Hz to 5GHz.

**Keyword:** - Analog to Digital Converter. CMOS process, low power comparator

## 1. Introduction

Designing of comparator with low power and high speed is a difficult challenge for low power applications. Mostly comparators are used in analog to digital converters. Comparator is also called as one bit analog to digital converter. Because comparator is a device that compares two voltages or currents and outputs a digital signal indicating which is larger. A comparator is made up of specialized differential amplifier. These are mostly used in devices which measures and convert analog signal into digital form such as ADC's (analog to digital converters), as well as relaxation oscillators. The rest of the paper is organized as follows. In section 2 we explain some of the existing dynamic latch comparators. Section 3 explains the proposed method to reduce the average power and static power. Section 4 contains the simulation results for the proposed method.

# 2. Conventional double tail dynamic latch comparator

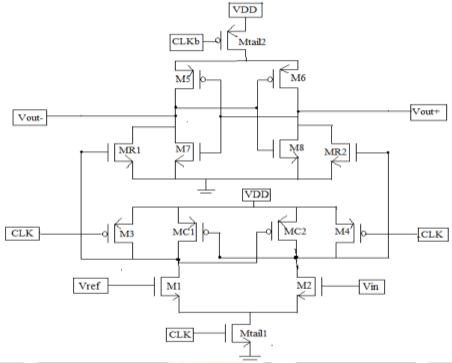

The Fig 1 shows the conventional double tail dynamic (clocked) latch comparator. It is similar to the basic comparator. In this comparator, transistors MC1 and MC2 are added with parallel to transistors M3 and M4 respectively.

This comparator has one disadvantage of high static power consumption. During decision phase, when Vin+ > Vin-, transistors M1, MC1 and Mtail turns ON. At this condition, VDD connects to GND which causes static power consumption. To overcome this problem, we added few transistors and proposed new comparator which gives best performance than other previous best design.

Fig -1: Conventional double tail dynamic latch comparator

# 3. Proposes dynamic latch comparator

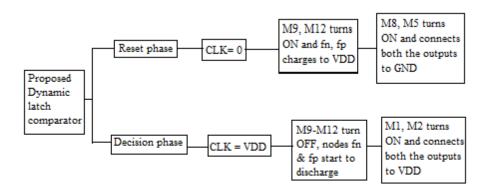

Now we are presenting a low power consumption dynamic latch comparator. The operation of this comparator is similar to the conventional dynamic latch comparator. But this comparator consumes less average power and static power. Fig 2 shows the design of proposed dynamic latch comparator. Working of this comparator is shown in block diagram below.

Fig- 2: Block diagram 1

Fig -3: Proposed dynamic latch comparator

# 3.1 Simulation results

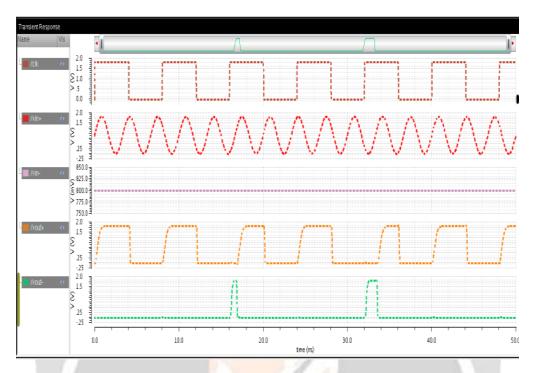

The simulation of the proposed comparator and existing comparator designs have been performed using Cadence tool and operations are performed using 180nm and 90nm technology. In order to compare other existing designs with our proposed design, we have taken some parameters like average and static power, propagation delay, PDP (power delay product), etc. The outputs are taken with 125MHz of clock frequency and 300MHz of input signal frequency.

# PINOS PINO PINOS P

# 3.2 CONVENTIONAL DYNAMIC LATCH COMPARATOR:

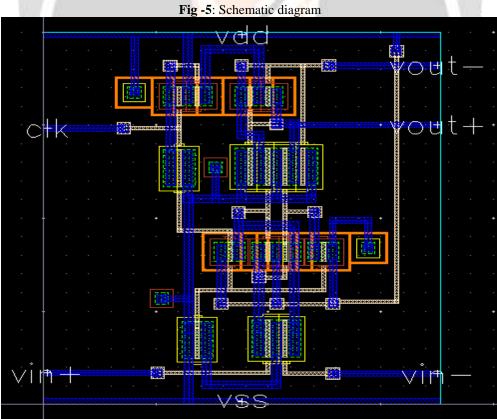

Fig -4: Schematic diagram

Fig -6: Layout diagram

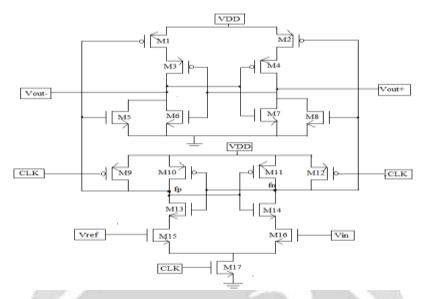

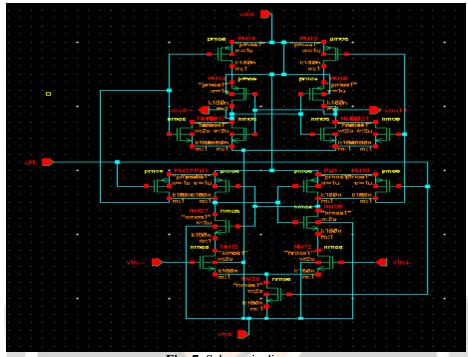

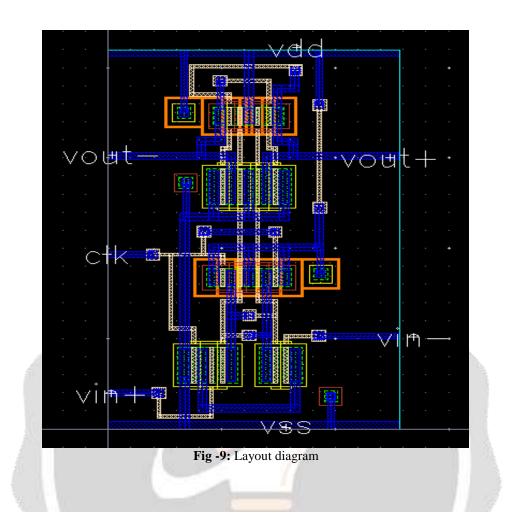

# 3.3 PROPOSED DYNAMIC LATCH COMPARATOR:

Fig -7: Schematic diagram

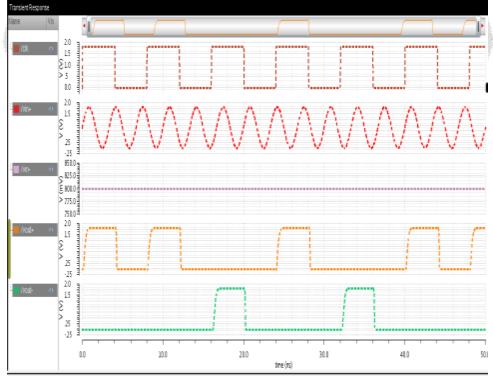

Fig -8: Output Waveform

**Table 1.** Performance comparison in 180nm (pre-layout).

| Design<br>specificatio<br>n | Conventio<br>nal<br>comparator | Compar<br>ator[1] | Compar<br>ator[2] | Propos<br>ed<br>comparato<br>r |

|-----------------------------|--------------------------------|-------------------|-------------------|--------------------------------|

| Average                     | 150.0E-6                       | 28.63E-6          | 31.56E-6          | 24.71E-6                       |

| power(w)                    |                                | 20.03E-0          | 31.30E-0          | 24./1E-0                       |

| Propagat                    | 1.267E-9                       |                   |                   |                                |

| ion delay(s)                |                                | 1.356E-9          | 1.335E-9          | 1.328E-9                       |

| $PDP_{avg}(J$               | 0.19E-12                       |                   |                   |                                |

| )                           |                                | 0.038E-12         | 0.041E-12         | 0.032E-12                      |

| Static                      | 45.95E-                        |                   |                   |                                |

| power(w)                    | 12                             | 50.94E-12         | 50.80E-12         | 28.91E-12                      |

| PDP <sub>static</sub> (     | 0.058E-                        |                   |                   |                                |

| J)                          | 18                             | 0.069E-18         | 0.067E-18         | 0.038E-18                      |

| No of                       | 16                             | 14                | 18                | 17                             |

| transistors                 |                                |                   |                   |                                |

**Table 2.** Performance comparison in 180nm (post-layout).

| Design<br>specificatio<br>n | Conventio<br>nal<br>comparator | Compar<br>ator[1] | Compar<br>ator[2] | Propos<br>ed<br>comparato<br>r |

|-----------------------------|--------------------------------|-------------------|-------------------|--------------------------------|

| Average                     | 150.0E-6                       |                   |                   |                                |

| power(w)                    |                                | 31.27E-6          | 32.53E-6          | 24.78E-6                       |

| Propagat                    | 1.254E-9                       |                   |                   |                                |

| ion delay(s)                |                                | 1.343E-9          | 1.343E-9          | 1.327E-9                       |

| $PDP_{avg}(J$               | 0.188E-12                      |                   |                   |                                |

| )                           |                                | 0.0419E-12        | 0.0431E-12        | 0.032E-12                      |

| No of                       | 16                             | 14                | 18                | 17                             |

| transistors                 |                                |                   |                   |                                |

**Table 3.**Comparison of proposed comparator with different input voltages.

| Design<br>specificati<br>on | 0.8v       | 1v     | 1.2v  | 1.4v  | 1.6v  |

|-----------------------------|------------|--------|-------|-------|-------|

| Averag                      | 3.74E      | 6.64E- | 10.54 | 14.54 | 19.24 |

| e                           | -6         | 6      | E-6   | E-6   | E-6   |

| power(w)                    |            |        |       |       |       |

| Propag                      | 1.56E      | 2.39E- | 2.693 | 1.182 | 1.278 |

| ation                       | <b>-</b> 9 | 9      | E-9   | E-9   | E-9   |

| delay(s)                    |            |        |       |       |       |

| PDP <sub>avg</sub> (        | 0.006      | 0.010  | 0.015 | 0.020 | 0.026 |

| J)                          | 4E-12      | 1E-12  | E-12  | 4E-12 | E-12  |

| Static                      | 9.945      | 13.18  | 16.68 | 20.46 | 24.53 |

| power(w)                    | E-12       | E-12   | E-12  | E-12  | E-12  |

| $PDP_{stati}$               | 0.014      | 0.018  | 0.023 | 0.028 | 0.033 |

| <sub>c</sub> (J)            | E-18       | E-18   | E-18  | E-18  | E-18  |

Table 4. Performance comparison in 90nm.

| Design<br>specificati<br>on | Conv<br>entional<br>compara<br>tor | Compar<br>ator[1] | Comp<br>arator[2] | Propo<br>sed<br>compara<br>tor |

|-----------------------------|------------------------------------|-------------------|-------------------|--------------------------------|

| Average                     | 5.968                              | 750.7E-           | 883.0             | 643.3                          |

| power(w)                    | E-6                                | 9                 | E-9               | E-9                            |

# 4. CONCLUSIONS

In this paper, a comprehensive analysis of power and delay for clocked dynamic comparators were done. Based on the analysis, a new dynamic comparator with low voltage, low power capability was proposed to improve the performance of comparator, mainly concerned in power consumption. Pre layout simulation results in 180nm and 90nm CMOS technology confirm that the power consumption of the proposed comparator is reduced to a great extent in comparison with all other dynamic comparators. And also the operational frequency of the proposed dynamic latch comparator is from 10Hz to 900MH.

## 5. REFERENCES

- [1]. Umamaheswari.V.S. and Rajaramya.V.G "Low Power High Performance Double tail comparator" International Journal of Scientific Engineering and Technology (ISSN: 2277-1581) Volume No.3 Issue No.5, pp: 647-650 1 May 2014 IJSET@2014 Page 648.

- [2]. Aparna Lahariya and Anshu Gupta "Design of Low Power and High Speed Dynamic Latch Comparator using 180 nm Technology", 2015 International Conference on Signal Processing, Computing and Control (2015 ISPCC), IEEE.

- [3]. Mr. Deepak Joseph Babu and Mr. Sunil Jacob "Design of a Low Voltage low Power Double tail comparator in 180nm cmos Technology", American Journal of Engineering Research (AJER) e-ISSN: 2320-0847 p-ISSN: 2320-0936 Volume-3, Issue-9, pp-15-19.

- [4]. Saurabh, A. Malik and P. Srivastava "New improved high speed low power double tail comparator design for 2.5 GHz input signal", students' Technology Symposium, pp. 205 209, March 2014.

- [5]. Gokul L, Jayachandran T and Marimuthu CN, "DESIGN OF DOUBLE TAIL COMPARATOR FOR ANALOG TO DIGITAL CONVERSION," UJEAS 2014, 02 (01): Page 63-66.

- [6]. Sanjay Kumar Jaiswal, Kumkum Verma, Gyanendra Singh and Neeraj Pratihar "Design of CMOS 8-BIT Comparator for Low Power Application", Fourth International Conference Computational Intelligence and Communication Networks (CICN), pp. 480 482, Nov. 2012.