# Design and analysis on the Performance of CNTFET Based Inverter in nanometer Regime

1.Ms. Bhavar Sonali R., E&TC, Matoshri College of Engineering, Nashik, India 2.Prof.Khule R.S., E&TC, Matoshri College of Engineering, Nashik, India

## **ABSTRACT**

In this paper we analyze PVT variation of CNTFET technology. In that we analyze performance of CNTFET inverter under the variation of temperature, supply voltage and oxide thickness. It's been observed that the effect of change in temperature, supply voltage and oxide thickness has little effect on rise and fall time of the inverter. The leakage power consumption of the CNFET inverter is very small and validate this comparison has been carried out for 32nm and 22nm technology. The influence of variation of parameters on the characteristics of CNTFET inverter is simulated and analyzed using H-SPICE tool and Stanford nano model-39 of CNTFET.

Keywords— Carbon nano-tube CNT, CNTFETs, temperature, supply voltage, oxide thickness.

## 1. Introduction

The scaling of devices has shrunk the device size considerably over the time and integration of number of transistors into the chip has increased drastically. As a consequence there is tremendous increase in leakage currents, high power consumption and reduced reliability of the devices. Silicon technology continues to scale down and is a dominant choice for high-performance digital circuits. These challenging aspects leads the researcher to investigate the performance of nano scaled devices. Carbon nanotubes (CNTs) have been explored as a promising candidate for the same. As CNTFETS whose diameter is ranging from 1 to 3 nm and the length can be up to several micrometers, CNTFETS can also be used as interconnections because of their higher carbon- carbon bond strength and scalable feature. The idea of implementing logic circuits with CNTFETS is to overcome the limitations of traditional silicon MOSFETS with modification in channel material by introducing a single CNT into the channel. As the MOSFET suffers with short channel effects due to scaling, the replacement of the channel with a CNT, not only facilitate the device to scale down to nano regime but also offers efficient performance due to its better electrical properties.

The effect of change in temperature and oxide thickness has little effect on rise and fall time of the inverter. The leakage power consumption of the CNTFET inverter is very small [1]. It is found that with decreasing in diameter power reduces but with a delay penalty [2-4]. CNTFET has some unique property of decreasing quantum capacitance, while reducing the thickness of oxide which is not possible in MOSFET [3]. and effect of variation of chiral vector on threshold voltage in CNTFET devices its found that at low value of chiral pair the threshold voltage is higher, whereas at high value of chiral vector the threshold voltage comes lower and the effect of temperature on threshold voltage is very less or negligibly small[3-5]. CNTFET inverter has ideal response with Vst=Vdd/2=0.6V whereas CMOS technology inverters switch at slightly higher values and has slower switching compared to CNTFET [6].The I-V characteristics of CNTFET are identical to that of MOSFET and the heavily doped CNTs are placed between gate and source/drain regions to have a low series resistance in ON state [7]. [8] Has analyzed using nanoHUB tools and justified the advantage of CNTFET device over MOSFET device in nanometer regime and concluded that the CNTFET has the potential to lead the post-CMOS device domain. The geometry-dependent threshold voltage of CNFETs has been effectively used to design a ternary logic family [10].

#### 1.1 Structure of Carbon Nano Tube Transistor

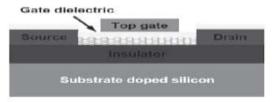

Fig.1 depicts the structure of a CNTFET device [3] the channel region under the gate dielectric of a conventional MOSFET has been replaced by a CNT. The length and diameter of the CNT will decide the feature size.

Fig. 1 Structure of CNTFET Device.

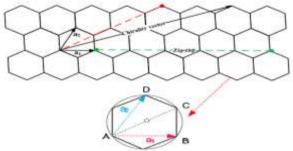

For determining the diameter of a SWCNT, we can draw a carbon molecule as a regular hexagon in a circle as shown in Fig.2 [11].

Fig.2 Unrolled graphite sheet.

In this figure triangular ABD is isosceles, so a1=a2. By considering the rectangular triangle ABC and by means of triangular relationship |a1| and |a2| is determined as:

$$a_1 - a_2 = 2a_0 \sin(60^\circ) = \sqrt{3}a_0$$

The chiral vector is calculated as:

$$Ch^2 = a_1^2 n_1^2 + a_2^2 n_2^2 + 2a_1 a_2 n_1 n_2 \cos(60^\circ)$$

$$Ch = \sqrt{3} a_0 \sqrt{n_1^2 + n_2^2 + n_1 n_2}$$

Where, a0 shows the carbon to carbon atom distance. The diameter of a CNT can be calculated according to the following relation

$$D_{CNT} = \frac{\sqrt{3} a_0 \sqrt{n_1^2 + n_2^2 + n_1 n_2}}{\pi}$$

....2

Structure and operation of the carbon nanotube field effect transistors are more similar to traditional silicon transistors but the conduction channel in CNTFETs is consists of semiconducting SWCNTs. Threshold voltage of a CNTFET is approximately calculated as:

calculated as:

$$Vth \approx \frac{E_g}{2e} = \frac{\sqrt{3} \ a_0 V_{\pi}}{3 \ eD_{CNT}} \approx \frac{0.43}{D_{CNT}(nm)}$$

....3

The energy bandgap (FG) in eV of CNT is given as [4]

For conduction to start, the barrier at source channel junction has to be overcome energy EG/2 (= $\Delta$ 1, say). As barrier height determines the threshold voltage of an FET.

Transconductance gm of a CNTFET is given by equation [12]

$$g_m = \frac{\mu \, (\frac{Cgg}{L})}{(\frac{V_{ds}}{L})}$$

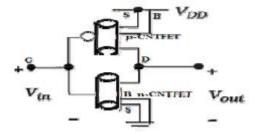

# 1.2 CNTFET Inverter

The digital inverter is the basic building block of logic circuits and it has been simulated in HSPICE with 32nm technology using Stanford models. The CNTFET inverter is depicted in Fig-3 is structurally identical to that of CMOS inverter except that the channel region is replaced by a SWCNT or MWCNT [6].p-CNTFET forms the pull up device and n-CNTFET forms the pull down device as depicted in fig.3.A pulsed signal with an initial value 0 volt and final value of 1 volt is provided at the gate terminal to observe the output and transfer characteristics of the circuit.

Fig. 3 CNTFET Inverter

## 2. H-SPICE Simulation analysis and result

In this analysis we have considered the model parameters as depicted in table1.Stanford model files were used and the standard model parameters considered for the design are depicted in table-1.

Table-1 Standard model parameters considered for the performance analysis of CNTFET inverter

| Sr.<br>No. | Parameter description        | value                 |

|------------|------------------------------|-----------------------|

| 1          | Supply voltage               | 0.4 volts             |

| 2          | Pitch                        | 20nm                  |

| 3          | Oxide thickness              | 1nm                   |

| 4          | Lch= Physical channel length | 32nm and 22nm         |

| 5          | Temperature                  | Between -80°C to 80°C |

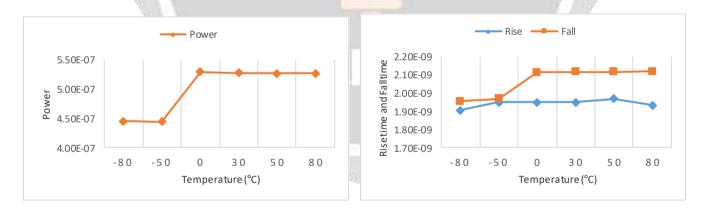

# 2.1 Effect of temperature on power and rise time and fall time of 32nm CNFET inverter:

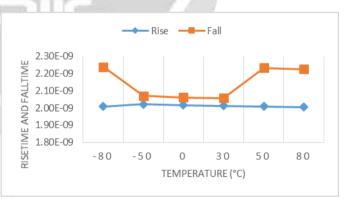

To analyze the inverter performance at different temperatures, 32nm and 22nm CNTFET inverter are designed and the temperature is varied between -80 to 80.

Fig-4 describes the variation of power with respect to variation of temperature for 32nm CNTFET.

Fig-5 describes the variation of Rise time and fall time of inverter with respect to variation of temperature for 32nm CNTFET.

Fig. 4 Variation of power with respect to temperature.

Fig. 5 Variation of rise time and fall time with respect to temperature.

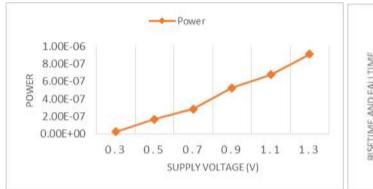

# 2.2 Effect of supply voltage on power and rise time and fall time of 32nm CNFET inverter

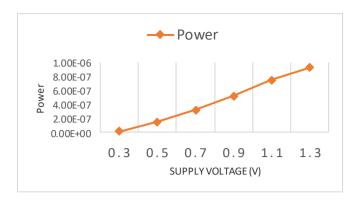

$Fig. 6 \ describes \ the \ variation \ of \ power \ with \ respect \ to \ variation \ of \ supply \ voltage \ for \ 32nm \ CNTFET.$

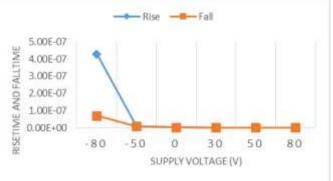

Fig-7 describes the variation of Rise time and fall time of inverter with respect to variation of supply voltage for 32nm CNTFET

Fig. 6 Variation of power with respect to supply voltage.

Fig. 7 Variation of rise time and fall with respect to supply voltage.

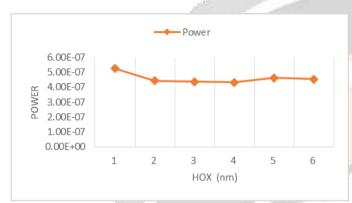

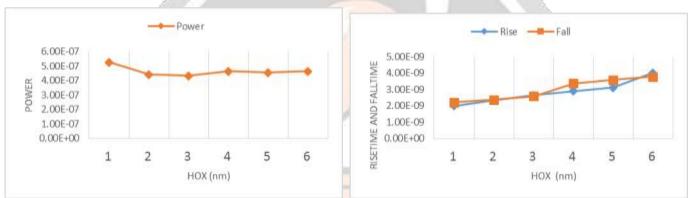

# 2.3 Effect of oxide thickness on power and rise time and fall time of 32nm CNFET inverter

Fig.8describes the variation of power with respect to variation of oxide thickness for 32nm CNTFET.

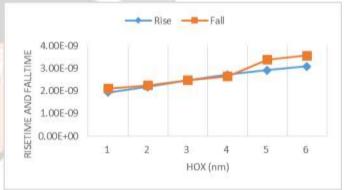

Fig-9 describes the variation of Rise time and fall time of inverter with respect to variation of oxide thickness for 32nm CNTFET.

Fig. 8 Variation of power with respect to oxide thickness.

Fig. 9 Variation of rise and fall time with respect to oxide thickness.

## 2.4 Effect of temperature on power and rise time and fall time of 22nm CNFET inverter

Fig-10 describes the variation of power with respect to variation of temperature for 22nm CNTFET.

Fig-11 describes the variation of Rise time and fall time of inverter with respect to variation of temperature for 22nm CNTFET.

Fig. 10 Variation of power with respect to temperature

Fig.11 Variation of rise and fall time with respect to temperature.

#### 2.5 Effect of supply voltage on power and rise time and fall time of 22nm CNFET inverter

Fig.12 describes the variation of power with respect to variation of supply voltage for 22nm CNTFET.

Fig-13 describes the variation of Rise time and fall time of inverter with respect to variation of supply voltage for 22nm CNTFET.

Fig. 12 Variation of power with respect to supply voltage.

Fig.13 Variation of rise and fall time with respect to supply voltage.

# 2.6 Effect of oxide thickness on power and rise time and fall time of 22nmCNFET inverter

Fig-14 describes the variation of power with respect to variation of oxide thickness for 22nm CNTFET. Fig-15 describes the variation of Rise time and fall time of inverter with respect to variation of oxide thickness for 22nm CNTFET.

Fig.14 Variation of power with respect to oxide thickness. Fig.15 Variation of rise and fall time with respect to oxide thickness.

The performance analysis of the CNTFET inverter reveals that it has very low power consumption and faster rise and fall time for its characteristics and assures it to be a promising candidate for the nano circuit design.

## 3. CONCLUSION

This paper compares the performance parameters of 32nm and 22nm CNFET inverter under variation of temperature, supply voltage and oxide thickness.

From fig.4, fig.6 and fig.8 it is evident that the power consumption of the inverter varies from  $0.44\mu W$  to  $0.52\mu W$ ,  $0.025\ \mu W$  to  $0.91\ \mu W$  and  $0.57\ \mu W$  to  $0.45\ \mu W$  respectively under temperature, supply voltage and oxide thickness variation. which reveals that the circuit consumes very low power. From fig.5, fig.7 and fig.9 we can infer that rise time(0 to  $90\ ^{\circ}/_{\circ}$ ) logic transition varies from 1.91ns to 1.93ns, 429ns to 1.49ns and 1.95ns to 3.10ns at minimum and maximum values of temperature, supply voltage and oxide thickness respectively.

Fall time (90 to  $10^{\circ}/_{\circ}$ ) of logic transition varies from 1.96ns to 2.12ns, 770ns to 1.51ns and 2.12ns to 3.58ns at minimum and maximum values of temperature, supply voltage and oxide thickness respectively. This reveals that CNTFET has near stable operation and reliable performance under temperature, supply voltage and oxide thickness variation. Further entire analysis is carried out again for 22nm technology. fig 10,11,12,13,14.15 depict the performance analysis for 22nm technology.

## 4. ACKNOWLEDGMENT

I take this OPPORTUNITY to express my heart-felt gratitude to my guide, Prof. R.S.Khule, for his constant encouragement, wonderful technical guidance and support throughout the course.

I express my thanks to all teaching & non-teaching staff of Electronics & telecommunication Department for their kind cooperation and guidance for preparing and presenting this seminar. I take this opportunity to express my gratitude towards my parents and my friends. Without which it would have not been possible.

#### 5. REFERANCES

- [1] Dr.Aswatha A R, Balaji Ramakrishna, "Impact of Temperature Variation and Oxide Thickness Variation on the Performance of CNTFET Based Inverter in nanometer Regime", International Conference on Emerging Research in Electronics, Computer Science and Technology, 978-1-4673-9563-2/15/\$31.00 ©2015 IEEE.

- [2] Sonal Shreya, Rajeevan Chandel, "Performance Analysis of CNTFET Based Digital Logic Circuits," Students Conference on Engineering and Systems (SCES), pp. 1-6, IEEE Conference Publications, May 2014.

- [3] Sanjeet Kumar Sinha, Saurabh Chaudhury, "Advantage of CNTFET Characteristics over MOSFET to Reduce Leakage Power," International Conference on Devices, Circuits and Systems (ICDCS), pp.: 1 5, DOI: 10.1109/ICDCSyst.2014.6926211 IEEE Conference Publications may 2014

- [4] RadhaTapiawala, "Performance Analysis of Logic Gates based on CNTFET"- International Journal for Scientific Research & Development Vol. 2, Issue 03, IJSRD 2014

- [5] Sanjeet Kumar Sinha, Saurabh Chaudhury, "Impact of Temperature Variation on CNTFET Device Characteristics", International conference on control, automation and robotics and embedded systems CARE- 978-1- 4673-6153 -8/13- IEEE Conference Publications 2013

- [6] Raghav Gupta, AshwaniK.Rana," Comparative Study of Digital Inverter for CNTFET & CMOS Technologies," Nirma university international conference on engineering, nuicone-2013, 28-30 november- 978-1-4673-1719--IEEE Conference Publications 2013

- [7] Sanjeet Kumar Sinha, Saurabh Chaudhury," Impact of Oxide Thickness on Gate Capacitance—A Comprehensive Analysis on MOSFET, Nanowire FET, and CNTFET Devices" Transactions on nanotechnology, vol. 12, no. 6, IEEE Conference Publications 2013

- [8] Sanjeet Kumar Sinha, Saurabh Chaudhury, "CNTFET: The Emerging Post-CMOS Device," 978-1-4799-1607/8/13 IEEE Conference Publications 2013

- [9] Sameer Prabhu, Nisha Sarwade, "Hspice Implementation of CNTFET Digital Gates", International Journal of Emerging Trends in Electrical and Electronics (IJETEE) ISSN: 2320-9569

- [10] A. Raychowdhury, K. Roy, "Carbon-nanotube-based voltage mode multiple-valued logic design," IEEE Trans. on Nanotechnology, vol. 4, no. 2, pp. 168 179, March 2005.

- [11] D. Devi, P. Rakesh, and V. Rakesh, "Impact of Scaling Gate Insulator Thickness on the Performance of Carbon Nanotube Field Effect Transistors (CNTFETs)," Nano and Electronic Physics, vol. 5, no. 2, 2013.

- [12] R. Sahoo and R. Mishra, "Simulations of Carbon Nanotube Field Effect Transistors," International Journal of Electronic Engineering Research, ISSN, pp. 117–125, 2009.

- [13] D. Zhou, T. J. Kazmierski, and B. M. Al-Hashimi, "Vhdlams implementation of a numerical ballistic cnt model for logic circuit simulation," in Specification, Verification and Design Languages, 2008. FDL 2008. Forum on. IEEE, 2008, pp. 94–98.

- [14] A. Lin, N. Patil, K. Ryu, A. Badmaev, L. De Arco, C. Zhou, S. Mitra, and H.-S. Wong, "Threshold voltage and on-off ratio tuning for multiple-tube carbon nanotube fets," Nanotechnology, IEEE Transactions on, vol. 8, no. 1, pp. 4–9, Jan 2009.

- [15] M. Fedawy, W. Fikry, A. Alhenawy, and H. Hassan, "Temperature effects on mosfet-like carbon nanotube field effect transistors," International Journal of Scientific and Engineering Research, vol. 4, no. 6, 2013.

- [16] A. Rahman, J. Guo, S. Datta, and M. Lundstrom, "Theory of ballistic nanotransistors," Electron Devices, IEEE Transactions on, vol. 50, no. 9, pp. 1853–1864, Sept 2003.

- [17] T. Kazmierski, D. Zhou, B. Al-Hashimi, and P. Ashburn,

- "Numerically efficient modeling of cnt transistors with ballistic and nonballistic effects for circuit simulation," Nanotechnology, IEEE Transactions on, vol. 9, no. 1, pp. 99–107, Jan 2010.

- [18] Q. Zhang, W. Zhao, and A. Seabaugh, "Low subthreshold- swing tunnel transistors," Electron Device Letters, IEEE, vol. 27, no.

- [19] R. Yousefi, "Effect of uniaxial strain on the subthreshold

- swing of ballistic carbon nanotube fets," Physica E: Lowdimensional Systems and Nanostructures, vol. 43, no. 10, pp. 1896–1901, 2011.