# REDUCED RATING DYNAMIC VOLTAGE RESTORER CONTROLLING WITH ENERGY OPTIMIZED

M. Chinmai<sup>1</sup>, KBVSR. Subrahmanyam<sup>2</sup>

<sup>1</sup>PG student [PE&ES], Department of EEE, SR Engineering College, Telangana State, India <sup>2</sup>Associate Professor, Department of EEE, SR Engineering College, Telangana State, India

# **ABSTRACT**

In this paper, By using the Voltage Source Converter in a Dynamic Voltage Restorer different types of voltage injection schemes are estimated with the minimization of the rating of the voltage source converter. A new control strategy is recommended to control the DVR which is supported with capacitor. The control of DVR is established with reduced rating VSC. The synchronous reference frame theory is used for the exchange of voltages from the rotating vectors to the stationary frame. The reference load voltage is projected using the unit vectors. The compensation technique of the voltage sag, swell and harmonics expected using a reduced rating of DVR.

**Keywords:** Dynamic voltage restorer, control strategy, power quality, unit vector, voltage sag, voltage swell.

# 1. INTRODUCTION

Power quality problems in the present day distribution systems are addressed in the literature [1-5] due to the increased use of sensitive and critical equipments such as communication network, process industries, precise manufacturing processes etc. Power quality problems such as transients, sags, swells and other distortions to the sinusoidal waveform of the supply voltage affect the performance of these equipments. The technologies such as custom power devices are emerged to provide protection against power quality problems [2]. Custom power devices are mainly of three categories such as series-connected compensators known as DVR (Dynamic Voltage Restorer), shunt connected compensators such as DSTATCOM (Distribution Static Compensator), and a combination of series and shunt-connected compensators known as UPQC (Unified Power Quality Conditioner) [2-5]. The DVR can regulate the load voltage from the problems such as sag, swell, harmonics etc. in the supply voltages. Hence it can protect the critical consumer loads from tripping and consequent losses [2]. The custom power devices are developed and installed at consumer point to meet the power quality standards such as IEEE-519 [6].

Voltage sags in an electrical grid are not always possible to avoid because of the finite clearing time of the faults that cause the voltage sags and the propagation of sags from the transmission and distribution systems to the low-voltage loads. Voltage sags are the common reasons for interruption in production plants and for end user equipment malfunctions in general. In particular, tripping of equipment in a production line can cause production interruption and significant costs due to loss of production. One solution to this problem is to make the equipment itself more tolerant to sags, either by intelligent control or by storing "ride-through" energy in the equipment. An alternative solution, instead of modifying each component in a plant to be tolerant against voltage sags, is to install a plant-wide uninterruptible power supply (UPS) system for longer power interruptions or a DVR on the incoming supply to mitigate voltage sags for shorter periods [7-22]. DVRs can eliminate most of the sags, and minimize the risk of load tripping for very deep sags, but their main drawbacks are their standby losses, the equipment cost and also the protection scheme required for downstream short circuits.

Many solutions and their problems using DVRs are reported such as the voltages in a three phase system are balanced [7] and an energy-optimized control of DVR is discussed in [9]. Industrial examples of DVRs are given in [10] and different control methods are analyzed for different types of voltage sags in [12-17]. A comparison of different topologies and control methods are presented for a DVR in [17]. The design of a capacitor supported DVR that protects sag, swell, distortion, or unbalance in the supply voltages is discussed in [15]. The performance of a DVR with the HFL (High Frequency Link) transformer is discussed in [22]. In this paper, the control and performance of a DVR are demonstrated with a reduced rating VSC (Voltage Source Converter). The SRF (Synchronous Reference Frame) theory is used for the control of the DVR.

# 2. OPERATION OF DVR

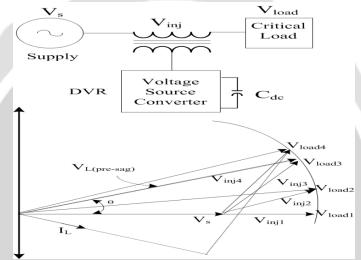

The schematic diagram of a DVR connected system is shown in Fig. 1 (a). The voltage  $V_{inj}$  is inserted such that the load voltage,  $V_{load}$  is constant in magnitude and undistorted, though the supply voltage  $V_s$  is not constant in magnitude or distorted. Fig.1(b) shows the phasor diagram of different voltage injection schemes of the DVR.  $V_{L(presag)}$  is a voltage across the critical load prior to the voltage sag condition. During the voltage sag, the voltage is reduced to  $V_s$  with a phase lag angle of  $\theta$ . Now the DVR injects a voltage such that the load voltage magnitude is maintained at the pre-sag condition. According to the phase angle of the load voltage, the injection of voltages can be realized in four ways [19].  $V_{inj1}$  represents the voltage-injected in-phase with the supply voltage. With the injection of  $V_{inj2}$ , the load voltage magnitude remains same but it leads  $V_s$  by a small angle. In  $V_{inj3}$ , the load voltage retains the same phase as that of the pre-sag condition, which may be an optimum angle considering the energy source [10].  $V_{inj4}$  is the condition where the injected voltage is in quadrature with the current and this case is suitable for a capacitor supported DVR as this injection involves no active power [17]. However, a minimum possible rating of the converter is achieved by  $V_{inj1}$ . The DVR is operated in this scheme with a BESS (Battery Energy Storage System).

Fig: 1- (a) Basic circuit of DVR, (b) Phasor diagram of the DVR voltage injection schemes.

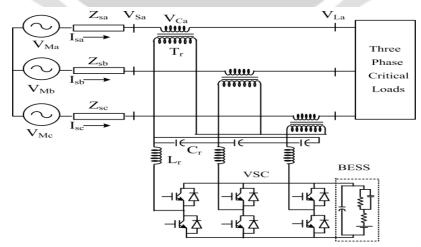

Fig. 2 shows a schematic diagram of a three-phase DVR connected to restore the voltage of a three phase critical load. A three phase supply is connected to a critical and sensitive load through a three phase series injection transformer. The equivalent voltage of the supply of phase A,  $(v_{Ma})$  is connected to the point of common coupling (PCC)  $(v_{Sa})$  through short circuit impedance  $(Z_{Sa})$ . The voltage injected by the DVR in phase A  $(v_{Ca})$  is such that the load voltage  $(v_{La})$  is of rated magnitude and undistorted.

Fig: 2- Schematic diagram of the DVR connected system.

A three phase DVR is connected to the line to inject a voltage in series using three single-phase transformers, Tr. Lr and Cr represent the filter components used to filter the ripples in the injected voltage. A three-leg VSC with IGBTs (Insulated Gate Bipolar Transistors) is used as a DVR and a BESS is connected to its dc bus.

#### 3. CONTROL OF DVR

The compensation for voltage sags using a DVR can be performed by injecting or absorbing the reactive power or the real power [17]. When the injected voltage is in quadrature with the current at the fundamental frequency, the compensation is made by injecting a reactive power and the DVR is with a self supported dc bus. But, if the injected voltage is in-phase with the current, DVR injects a real power and hence a battery is required at the dc bus of VSC. The control technique adopted should consider the limitations such as the voltage injection capability (converter and transformer rating) and optimization of the size of energy storage.

# 3.1. Control of DVR with BESS for Voltage Sag, Swell and Harmonics Compensation

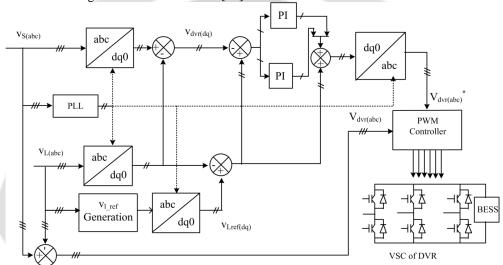

Fig. 3 shows a control block of the DVR in which SRF theory is used for reference signal estimation. The voltages at PCC (vs) and at load terminal (vL) are sensed for deriving the IGBTs gate signals. The reference load voltage ( $V_{L*}$ ) is extracted using the derived unit vector [23].

Fig: 3- Control block of the DVR which use the SRF method of control.

Load voltages ( $V_{La}$ , $V_{Lb}$ , $V_{Lc}$ ) are converted to the rotating reference frame using *abc-dqo* conversion using Park's transformation with unit vectors ( $\sin \theta$ ,  $\cos \theta$ ) derived using a PLL (phase locked loop) as,

$$\begin{bmatrix} v_{l,q} \\ v_{l,d} \\ v_{l,o} \end{bmatrix} = \frac{2}{3} \begin{bmatrix} \cos \theta & \cos \left(\theta - \frac{2\pi}{3}\right) & \cos \left(\theta + \frac{2\pi}{3}\right) \\ \sin \theta & \sin \left(\theta - \frac{2\pi}{3}\right) & \sin \left(\theta + \frac{2\pi}{3}\right) \end{bmatrix} \begin{bmatrix} v_{l,coref} \\ v_{l,bref} \\ v_{l,coref} \end{bmatrix}$$

$$\frac{1}{2} \qquad \frac{1}{2} \qquad \frac{1}{2} \qquad \frac{1}{2} \qquad (1)$$

Similarly, reference load voltages  $(V_{La^*}, V_{Lb^*}, V_{Lc^*})$  and voltages at PCC (vs) are also converted to the rotating reference frame. Then, the DVR voltages are obtained in the rotating reference frame as,

$$v_{Dd} = v_{Sd} - v_{Ld} \tag{2}$$

$$v_{Dq} = v_{Sq} - v_{Lq} \tag{3}$$

The reference DVR voltages are obtained in the rotating reference frame as,

$$v_{Dd} = v_{Sd} - v_{Ld}$$

(4)

$v_{Dq}^* = v_{Sq}^* - v_{Lq}$  (5)

The error between the reference and actual DVR voltages in the rotating reference frame are regulated using two PI (Proportional-Integral) controllers.

Reference DVR voltages in abc frame are obtained from a reverse Park's transformation taking  $V_{Dd^*}$  from (4),  $V_{Dq^*}$  from (5),  $V_{D0^*}$  as zero as,

$$\begin{bmatrix} v_{dn'a}^{*} \\ v_{dn'b}^{*} \\ v_{dn'c}^{*} \end{bmatrix} = \begin{bmatrix} \cos\theta & \sin\theta & 1 \\ \cos\left(\theta - \frac{2\pi}{3}\right) & \sin\left(\theta - \frac{2\pi}{3}\right) & 1 \\ \cos\left(\theta + \frac{2\pi}{3}\right) & \sin\left(\theta + \frac{2\pi}{3}\right) & 1 \end{bmatrix} \begin{bmatrix} v_{Dq}^{*} \\ v_{Dd}^{*} \\ v_{D0}^{*} \end{bmatrix}$$

(6)

Reference DVR voltages (Vdvra\*, Vdvrb\*, Vdvrc\*) and actual DVR voltages (Vdvra, Vdvrb, Vdvrc) are used in a PWM controller to generate gating pulses to a VSC of DVR. The PWM controller is operated with a switching frequency of 10 kHz.

# 3.2. Control of Self Supported DVR for Voltage Sag, Swell and Harmonics Compensation

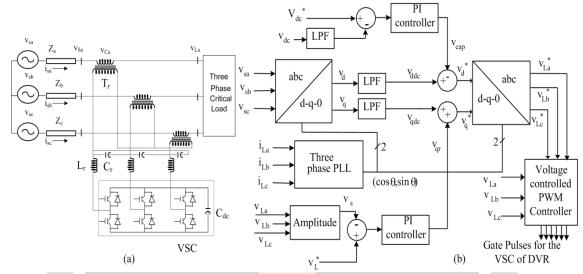

**Fig: 4-** (a) Schematic diagram of self supported DVR (b) Control block of the DVR which uses the SRF method of control.

Fig. 4(a) shows a schematic diagram of a capacitor supported DVR connected to three phase critical loads and Fig. 4(b) shows a control block of the DVR in which SRF theory is used for the control of self supported DVR. Voltages at PCC (vs) are converted to the rotating reference frame using *abc-dqo* conversion using the Park's transformation. The harmonics and the oscillatory components of the voltage are eliminated using LPFs (Low Pass Filters). The components of voltages in d-axis and q-axis are,

$$v_d = v_{ddc} + v_{dac}$$

$$v_q = v_{qdc} + v_{qac}$$

(7)

(8)

The compensating strategy for compensation of voltage quality problems considers that the load terminal voltage should be of rated magnitude and undistorted. In order to maintain the dc bus voltage of the self-supported capacitor, a PI controller is used at the dc bus voltage of DVR and the output is considered as a voltage  $(v_{cap})$  for meeting its losses.

$$v_{cap(n)} = v_{cap(n-1)} + K_{pl}(v_{de(n)} - v_{de(n-1)}) + K_{il}v_{de(n)}$$

(9)

where, is the error between the reference ( $v_{dc}^*$ ) and sensed dc voltage ( $v_{dc}$ ) at the  $n_{th}$  sampling instant.  $K_{p1}$  and  $K_{i1}$  are the proportional and the integral gains of the dc bus voltage PI controller.

The reference d-axis load voltage is, therefore, as,

$$v_d^* = v_{ddc} - v_{cap} \tag{10}$$

The amplitude of load terminal voltage ( $V_L$ ) is controlled to its reference voltage ( $V_{L^*}$ ) using another PI controller. The output of PI controller is considered as the reactive component of voltage ( $v_{qr}$ ) for voltage regulation of the load terminal voltage. The amplitude of load voltage ( $V_L$ ) at PCC is calculated from the ac voltages ( $v_{La}$ ,  $v_{Lb}$ ,  $v_{Lc}$ ) as,

$$V_{L} = (2/3)^{1/2} (v_{La}^{2} + v_{Lb}^{2} + v_{Lc}^{2})^{1/2}$$

(11)

Then, a PI controller is used to regulate this to a reference value as,

$$v_{qr(n)} = v_{qr(n-1)} + K_{p2}(v_{te(n)} - v_{te(n-1)}) + K_{i2}v_{te(n)}$$

(12)

where, denotes the error between reference ( \*) and actual ( ) load terminal voltage amplitudes at  $n_{th}$  sampling instant.  $K_{p2}$  and  $K_{i2}$  are the proportional and the integral gains of the dc bus voltage PI controller.

The reference load quadrature axis voltage is as,

$$v_q^* = v_{qdc} + v_{qr} \tag{13}$$

Reference load voltages (VLa\*, VLb, VLc\*) in abc frame is obtained from a reverse Park's transformation as in (6). The error between sensed load voltages (VLa, VLb, VLc) and reference load voltages are used over a controller to generate gating pulses to VSC of DVR.

# 4. SIMULATION RESULTS OF DVR SYSTEM

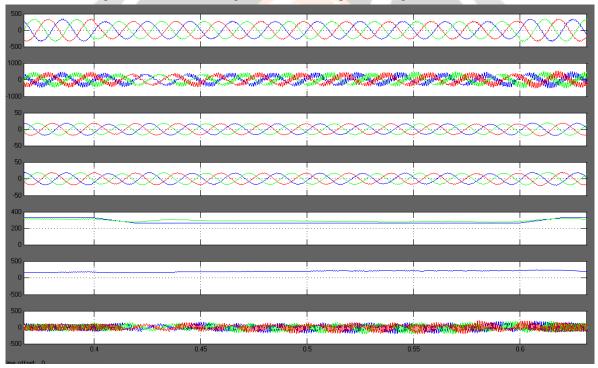

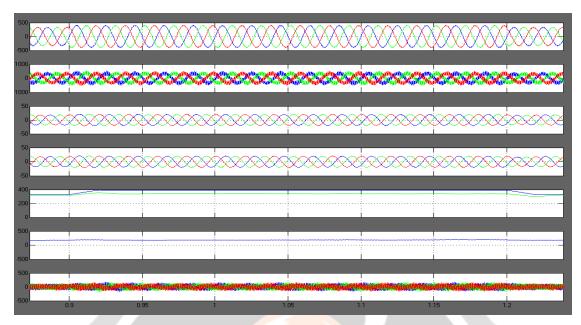

The performance of the DVR is demonstrated for different supply voltage disturbances such as voltage sag and swell. Fig. 5(a) & 5(b) shows the transient performance of the system under voltage sag and voltage swell conditions. At 0.2 s, a sag in supply voltage is created for 5 cycles and at 0.4 s, a swell in the supply voltages is created for 5 cycles. It is observed that the load voltage is regulated to constant amplitude under both sag and swell conditions. Source voltage ( $V_{\text{sabc}}$ ), Load voltage ( $V_{\text{Labc}}$ ), Source current ( $I_{\text{Sabc}}$ ), Load current ( $I_{\text{Labc}}$ ), Terminal voltage ( $V_{\text{tms}}$ ), DC-Link voltage ( $V_{\text{DC}}$ ) and DVR voltage ( $V_{\text{dvr}}$ ) are also depicted in Fig. 5(a) & 5(b).

**Fig: 5(a)-** Dynamic results of DVR under voltage sag condition- Source voltage  $(V_{sabc})$ , Load voltage  $(V_{Labc})$ , Source current  $(I_{Sabc})$ , Load current  $(I_{Labc})$ , Terminal voltage  $(V_{tms})$ , DC-Link voltage  $(V_{DC})$  and DVR voltage  $(V_{dvr})$ .

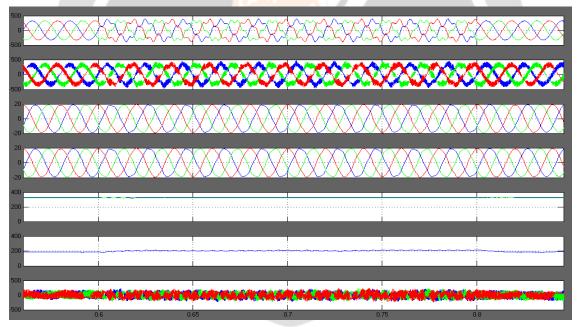

The compensation of harmonics in the supply voltage is demonstrated in Fig. 6. At 0.2 s, the supply voltage is distorted and continued for 5 cycles. The load voltage is maintained sinusoidal by injecting proper compensation voltage by the DVR. The magnitudes of the voltage injected by the DVR for mitigating the same kinds of sag in the supply with different angle of injection are observed. The injected voltage, series current and kVA ratings of the DVR for the four injection schemes are given in Table-I. In Scheme-1 of Table-1, the in-phase injected voltage is Vinj1 in the phasor diagram of Fig.1. In Scheme-2, a DVR voltage is injection at a small angle of 30° and in Scheme-3 is the DVR voltage is injected at an angle of 45°. The injection of voltage in quadrature with the line current is in Scheme-4. It is observed that the injected voltage is in quadrature with the supply current and hence a capacitor can support the dc bus of DVR. But, the injected voltage is higher compared to an in-phase injection (Scheme-1).

Fig: 5(b)- Dynamic results of DVR under voltage Swell condition- Source voltage ( $V_{sabc}$ ), Load voltage ( $V_{Labc}$ ), Source current ( $I_{Sabc}$ ), Load current ( $I_{Labc}$ ), Terminal voltage ( $V_{tms}$ ), DC-Link voltage ( $V_{DC}$ ) and DVR voltage ( $V_{dvr}$ ).

Fig: 6- Simulation results of dynamic performance of DVR during harmonics in supply voltage- Source voltage  $(V_{sabc})$ , Load voltage  $(V_{Labc})$ , Source current  $(I_{Sabc})$ , Load current  $(I_{Labc})$ , Terminal voltage  $(V_{tms})$ , DC-Link voltage  $(V_{DC})$  and DVR voltage  $(V_{dvr})$ .

# 5. CONCLUSION

The operation of a DVR has been demonstrated with a new control technique using various voltage injection schemes. A comparison of the performance of DVR with different schemes has been performed with reduced rating VSC including capacitor supported DVR. The reference load voltage has been estimated using the method of unit vectors and the control of DVR has been achieved which minimizes the error of voltage injection. The SRF (Synchronous Reference Frame) theory has been used for estimating the reference DVR voltages. It is concluded that the voltage injection in-phase with the PCC voltage results in minimum rating of DVR but at the cost of an energy source at its dc bus.

# REFERENCES

- [1] Math H.J. Bollen, Understanding Power Quality Problems- Voltage Sags and Interruptions, IEEE Press, New York, 2000.

- [2] A. Ghosh and G. Ledwich, Power Quality Enhancement using Custom Power devices, Kluwer Academic Publishers, London, 2002.

- [3] Math H. J. Bollen and Irene Gu, Signal Processing of Power Quality Disturbances, Wiley-IEEE Press, 2006.

- [4] R. C. Dugan, M. F. McGranaghan and H. W. Beaty, Electric Power Systems Quality. 2nd Edition, New York, McGraw Hill, 2006.

- [5] K.R. Padiyar, FACTS Controllers in Transmission and Distribution, New Age International, New Delhi, 2007.

- [6] IEEE Recommended Practices and Recommendations for Harmonics Control in Electric Power Systems, IEEE Std. 5 19, 1992.

- [7] V B Bhavraju and P N Enjeti, "An active line conditioner to balance voltages in a three phase system", IEEE Trans. Ind. Appl., vol. 32, no. 2, 1996, pp. 287-292.

- [8] S. Middlekauff and E. Collins, "System and customer impact," IEEE Trans. on Power Del., vol. 13, no. 1, pp. 278–282, Jan. 1998.

- [9] M. Vilathgamuwa, R. Perera, S. Choi and K. Tseng, "Control of energy optimized dynamic voltage restorer," in Proc. IEEE IECON'99, vol. 2,1999, pp. 873–878.

- [10] J. G. Nielsen, F. Blaabjerg, and N. Mohan, "Control strategies for dynamic voltage restorer compensating voltage sags with phase jump," in Proc. IEEE APEC'01, vol. 2, 2001, pp. 1267–1273.

- [11] A. Ghosh and G. Ledwich, "Compensation of distribution system voltage using DVR", IEEE Trans. on Power Delivery, vol. 17, no. 4, pp. 1030 1036, Oct. 2002.

- [12] A. Ghosh and Joshi A, "A new algorithm for the generation of reference voltages of a DVR using the method of instantaneous symmetrical components", IEEE Power Engineering Review, vol. 22, no.1, pp. 63 65, Jan. 2002.

- [13] Eddy C. Aeloíza, Prasad N. Enjeti, Luis A. Morán, Oscar C. Montero-Hernandez, and Sangsun Kim, "Analysis and Design of a New Voltage Sag Compensator for Critical Loads in Electrical Power Distribution Systems", IEEE Trans. on Ind. Appl., vol. 39, no. 4, pp 1143-1150, Jul/Aug 2003.

- [14] J. W. Liu, S.S. Choi and S. Chen, "Design of step dynamic voltage regulator for power quality enhancement", IEEE Trans. on Power Delivery, vol. 18, no.4, pp. 1403 1409, Oct. 2003.

- [15] Arindam Ghosh, Amit Kumar Jindal and Avinash Joshi, "Design of a capacitor supported dynamic voltage restorer for unbalanced and distorted loads" IEEE Trans. on Power Delivery, vol.19, no. 1, pp. 405-413, Jan 2004.

- [16] A. Ghosh, "Performance study of two different compensating devices in a custom power park", IEE Proc. on Generation, Transmission and Distribution, vol. 152,no. 4, pp. 521 528, July 2005.

- [17] John Godsk Nielsen and Frede Blaabjerg, "A detailed comparison of system topologies for dynamic voltage restorers", IEEE Trans. on Ind. Appl., vol. 41, no. 5, pp.1272-1280, Sept/Oct. 2005.

- [18] M.R. Banaei, S.H. Hosseini, S. Khanmohamadi and G.B. Gharehpetian, "Verification of a new energy control strategy for dynamic voltage restorer by simulation", Simulation Modeling Practice and Theory, vol.14, no. 2, pp. 112-125, February 2006.

- [19] Amit Kumar Jindal, Arindam Ghosh and Avinash Joshi, "Critical load bus voltage control using DVR under system frequency variation", Electric Power Systems Research, vol.78, no.2, pp. 255-263, 2008.

- [20] D. Mahinda Vilathgamuwa H. M. Wijekoon, and S. S. Choi, "A Novel Technique to Compensate Voltage Sags in Multiline Distribution System—The Interline dynamic Voltage Restorer", IEEE Transactions on Industrial Electronics, vol. 54, no. 4, pp.1603-1611, August 2007.

- [21] A. Chandra, B. Singh, B.N. Singh and K. Al-Haddad, "An improved control algorithm of shunt active filter for voltage regulation, harmonic elimination, power-factor correction, and balancing of nonlinear loads", IEEE Trans. on Power Electronics, vol. 15, no. 3, pp. 495 507, May 2000.

- [22] Ali Yazdanpanah Goharrizi, Seyed Hossein Hosseini, Mehran Sabahi, and Gevorg B. Gharehpetian, "Three-Phase HFL-DVR With Independently Controlled Phases," IEEE Trans on Power Electronics vol. 27, no.4, pp. 1706-1718, April 2012.