# A Study of Use of QCA Technology for Nano Circuit Libraries

# Murali Kattamuri<sup>1</sup>, Dr. Subhashish Bose<sup>2</sup>

<sup>1</sup>Research Scholar, Department of Electronics and Communication Engineering, Sri Satya Sai University of Technology & Medical Sciences, Sehore, M.P., India.

<sup>2</sup>Research Supervisor Department of Electronics and Communication Engineering, Sri Satya Sai University of Technology & Medical Sciences, Sehore, M.P., India.

## Abstract

The proposed research work uses the QCA technology to design digital circuits in an optimized manner at the nano level. Initially, the conventional structures such as 2's complement adder and subtract or, Baugh-Wooley multiplier is presented to exploit the advantages of QCA. Afterwards, various existing XOR gate structures are analyzed. It is identified that there is a possibility to optimize the XOR gate layout. So, an enhanced XOR gate layout structure is presented in a single layer. The XOR gate structure is more significant in many applications such as a Half Adder, Full Adder, Equality Byte Comparator, Parity generator and checker, etc.,. All these applications are implemented by enhanced XOR gate layout structure. The proposed structures are implemented without using crossovers, which reduces the number of cells required and performs the functionality in a cost efficient manner with higher speed. Over the latest twenty years, contemporary Complementary Metal Oxide Semiconductor (CMOS) circuits overpowered the Integrated Circuit (IC) innovation in a quick way. The XOR entryway structure is huger in various applications, for instance, a Half Adder, Full Adder. All of these applications is realized by improved XOR gate design structure. The proposed structures are realized without using mixtures, which reduces the amount of cells required and plays out the handiness in a cost beneficial manner with higher speed. A brief timeframe later, unique existing XOR gate structures are analyzed. It is perceived that there is probability to smooth out the XOR entryway design. Thusly, an upgraded XOR gate configuration structure is presented in a lone layer.

Keyword: Complementary, Configuration, Structure, Adder.

# 1. INTRODUCTION

The Integrated Circuit (IC) technology is tremendously growing day by day to improve the performance of the CMOS technology in a compact and high-density form. The traditional CMOS technology faces some of the limitations, such as short channel effects and quantum effects, etc. Therefore, there is a necessity for alternate devices to CMOS as well as to build the digital circuits at Nano-scale. Hence, a new tiny IC arena introduced by Lent et al., is the Quantum-dot Cellular Automata (OCA) to overcome the pitfalls of conventional CMOS technology. With the advent of a new form of IC design brings a new way of binary computing using QCA for highperformance digital circuits compared to the existing Nano-computing devices. An optimized logic circuit can be designed by using the majority gates, inverter and binary wires using OCA cells in an appropriate combination. For developing new and helpful advancements for designing Nano-scale circuits, some new courses of action should be considered. Advancements, for instance, single-electron semiconductor, Nano Carbon tubes, nuclear switches, etc. are a segment of the possible courses of action. Similarly, in the continuous years various experts have been inspected to design Nano-scale circuits using Quantum Cellular Automata (QCA) innovation and scientists and originators of the modernized circuit believe that CMOS will be replaced with this novel innovation. Basic action and limit of a QCA cell have been exhibited and genuinely completed in the late of 1990's. Starting now and into the foreseeable future, different designs reliant on QCA have been proposed. These designs consolidate not simply little designs, for instance, an Adder or XOR yet in addition huge designs, for instance, a processor. This part presents OCA innovation and sorts of deformations that may occur in this innovation.

# 2. LITERATURE REVIEW

Banik, Debajyoty (2015) Quantum PC is very pattern setting development in impending period and can ready to deal with any flighty issue with especially speedy estimation power. The proposed models for quantum count are quantum speck cell automata (QCA). The nuclear QCA will in general high bungle rates. On the off chance that there should be an event of sub-nuclear quantum dab cell automata, the rule focus of circuit configuration is the diminishing of circuit locale with required helpful direct.

Vijay Kumar Sharma (2017) Quantum spot cell automata (QCA) is a transistor-less innovation to execute the nanoscale circuit designs. QCA circuits are fast, significantly thick and scatter less energy when diverged from commonly used corresponding metal oxide semiconductor (CMOS) innovation. In this paper, a novel structure for advanced comparator using QCA nanotechnology is proposed. Advanced comparator is a fundamental and huge module in central getting ready unit which considers two paired numbers.

Kumar (2014) Quantum-speck cell automata (QCA) has emerged as a dire choice as opposed to CMOS innovation in the progressing years. In any case, the basic anticipation in movement of QCA innovation is that it encounters various types of amassing disfigurements and assortments. A couple of cell dispersing relinquishes introduced in the declaration period of gathering pattern of QCA have been found to be normal.

Abutaleb, Mostafa (2018) among various nanotechnology gadgets, single-electron tunneling gadgets are the most promising chance to substitute the present CMOS gadgets. In this paper, another single-electron limit reasoning circuit module is presented for recognizing and completing Nano-electronic circuits. The proposed module can be dedicated to realize all basic reasoning entryways, for instance, OR, NOR, AND, NAND, XOR and XNOR gates, that can be composed in various propensities to configuration modernized circuits.

Abdullah-Al-Shafi, (2017) Force usage in irreversible QCA reasoning circuits is an irreplaceable and a huge issue; at any rate in the judicious cases, this middle is by and large overlooked. The total power weariness dataset of different QCA multiplexers have been worked out in this paper. At -271.15 °C temperature, the consumption is surveyed under three separate tunneling energy levels. All the circuits are designed with QCA Designer, a broadly used reenactment engine and QCA Pro gadget has been applied for surveying the power dispersal.

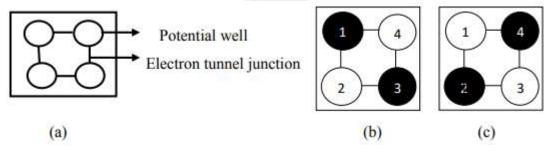

## 3. PREREQUISITES OF QCA

A new physical structure for a digital design that offers novel computing architecture is Quantum-Dot Cellular Automata (QCA) technology. In QCA, logic states are stored depending on the position of individual electrons, but not based on voltage levels. In general, QCA represents binary information by utilizing a bistable charge configuration. Therefore, QCA cell is locked with two electrons, which exist in the potential wells in diagonal positions because of the Coulombic repulsion. The potential wells are linked through the electron tunnel junctions as shown in Figure 1(a). The tunnelling of electrons between the potential wells is achieved by the application of the suitable potential. The positions of diagonally occupied two mobile electrons represent binary information as logic '0' and logic '1' as shown in Figure 1 (b) and 1(c) respectively.

Fig 1 (a) Anatomy of a QCA cell (b) QCA with logic 0 (c) QCA with logic 1

#### Half Adder

In the current Half Adder structures, the XOR gate was created by standard method and entire was cultivated clearly from the yield of XOR entryway, anyway an additional entryway is expected to convey pass on with the utilization of the multilayer structure. In any case, using the Equation, both XOR gate value and Half Adder value can be obtained in a comparable circuit.

#### **Full Adder**

The current design uses two entryways moreover to create the yield pass on. However, the pass on path in the proposed Full Adder configuration is improved by using the upgraded XOR coordinated Half Adder. It requires seven dominant part entryways and two inverters without half breeds. It evades additional predominant part entryways and mixtures diverged from the current design.

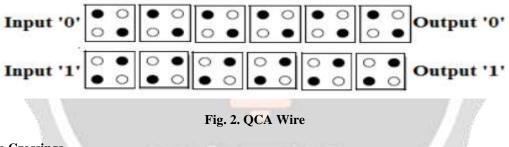

#### QCA Wire

A series of cells can be used as interconnection wire as shown in Figure 2 [1]. The propagation of the signal from one end (input) to the other end (output) takes place because of Coulombic repulsion between the adjacent cells. As the computations in QCA technology is performed using an array of the quantum devices the inner cells have no direct contact; so the information or energy can pass in the array only from the edges. Therefore, computing in a QCA paradigm is edge driven. Edge-driven computation requires neither energy nor information to be transmitted directly to interior cells. The energy needed to set each input in the array about 1meV / input bit [1]. Hence, the transfer of binary information in QCA technology is very attractive compared to the CMOS technology.

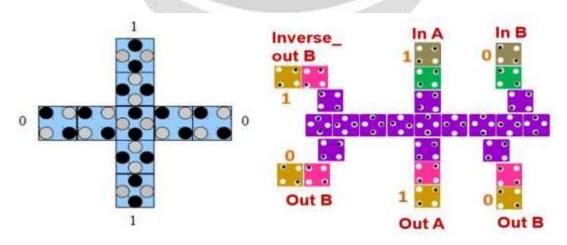

#### **QCA Wire Crossings**

The wire crossings in QCA are two types named as a coplanar crossover, multilayer crossover. The coplanar crossover utilizes both regular and 450 rotated cells within the layer as shown in Figure 3 [2]. Research on wire crossings in QCA design has identified the sensitive behavior of coplanar crossover to misalignment and susceptible to noise.

#### Fig. 3 Coplanar crossover

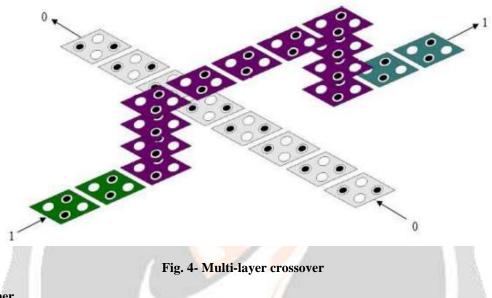

The limitations of the coplanar crossover can be overcome with the multi-layer crossover. The structure of multilayer wire crossing is similar to the bridge as shown in Figure 4. The multilayer wire crossover has more than one layer of cells similar to the routing of metal wire crossings in CMOS technology. The multi-layer crossover achieves more reliable wire crossing compared to the coplanar crossover. The proposed designs in this thesis are constructed using multi-layer wire crossing. In this work, multi-layer wire crossings are used to construct the designs.

#### **QCA Designer**

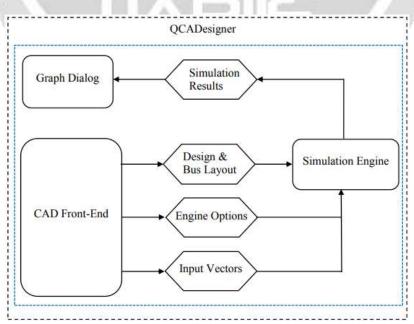

Initially, The University of Calgary, at Advanced Technology Information Processing Systems (ATIPS) Laboratory, Canada, developed the QCA Designer. Later, it was attracted the new developers and researchers from the University of Notre Dame, Notre Dame [21]. QCA Designer is a Computer Aided Design (CAD) tool specifically designed for QCA logic circuit layout design and simulation. The design and data flow in QCA Designer is shown in Figure 5.

#### Fig. 5 QCA Designer design flow

The front end of the QCA Designer toolbox, which facilitates quick and rapid design capability for the user. The front end links the list of cells, options to select simulation engine and choice of the input vector. Once the constructed design is simulated, it displays the simulation results in a separate window in a graph dialog. Some of the important features of QCA Designer include:

- Add/remove cells;

- ¬ Move/scale/rotate cells;

- $\neg$  Create input/output cells;

- $\neg$  Create arrays of cells;

- Group input, output and intermediate cells into digital buses;

- $\neg$  Create/edit input and output labels;

- ¬ PostScript printing;

- $\neg$  Ability to merge designs.

## 4. CONCLUSION

In this part, we presented an improved XOR door structure and its applications. The employments of XOR door structure, for instance, Half Adder, Full Adder, are presented. The proposed circuit designs are clear in structure with the most un-possible number of cells and with less deferral. In this part, the proposed designing XOR entryway is executed in a single layer structure rather than using the half and halves and achieved enormous improvement in execution. The introduction relationship of different uses of XOR doors created using QCA is explained in detail. The plan and organization of Half Adder, Full Adder is presented in definite reliant on improved XOR course of action. The XOR entryway and its applications were improved and created in a lone layer structure.

### **5. REFERENCES**

- 1. Abdullah-Al-Shafi, Md &Bahar, Ali Newaz& Zahoor, Peer & Ahmad, Firdous & Bhuiyan, Mohammad. (2017). Power analysis dataset for QCA based multiplexer circuits.

- 2. Abdullah-Al-Shafi, Md & Islam, Md &Bahar, Ali Newaz. (2015). A Review on Reversible Logic Gates and its QCA Implementation. International Journal of Computer Applications (IJCA).

- 3. Abdullah-Al-Shafi, Md. (2016). Analysis of Fredkin Logic Circuit in Nanotechnology: An Efficient Approach. International Journal of Hybrid Information Technology.

- 4. Abutaleb, Mostafa. (2018). Design and Simulation of Single-electron Tunneling based Nano-electronics Circuits. Communications on Applied Electronics.

- 5. Banik, Debajyoty. (2017). Online Testable Efficient Latches for Molecular QCA Based on Reversible Logic.

- 6. Vijay Kumar Sharma (2017) Optimal design for digital comparator using QCA nanotechnology with energy estimation. International Journal of Numerical Modelling: Electronic Networks, Devices and Fields Early View.

- 7. Kumar, Dharmendra & Mitra, Debasis. (2014). A systematic approach towards fault-tolerant design of QCA circuits. Analog Integrated Circuits and Signal Processing.

- 8. Suresh, Muchharla& Panda, Ajit&Sukla, Mukesh &Vasanthi, Marakonda&Santhi, Sowpati. (2016). Analysis of CMOS and MTCMOS Circuits Using 250 Nano Meter Technology.

- 9. Sofeoul-Al-Mamun, Md & Miah, Md Badrul& Al Masud, Fuyad. (2017). A Novel Design and Implementation of 8-3 Encoder Using Quantum-dot Cellular Automata (QCA) Technology. European Scientific Journal.

- 10. Sinha Roy, Soudip& Mukherjee, Chiradeep& Panda, Saradindu& Mukhopadhyay, Asish& Maji, Bansibadan. (2017). Layered T Comparator using Quantum Cellular Automata.