# DESIGN OF POWER EFFICIENT DOUBLE TAIL DYNAMIC COMPARATOR

Puppala Abhilash<sup>1</sup>, M.Sirinkumari<sup>2</sup>

<sup>1</sup> Student, Sree Chaitanya Institute Of Tech. Sciences, Karimnagar, Telangana, INDIA <sup>2</sup> Assistant Professor, Sree Chaitanya Institute Of Tech Sciences, Karimnagar, Telangana, INDIA

#### **ABSTRACT**

In recent years, there has been an increasing demand for high-speed digital circuits at low power consumption. This need for ultra-low-power, area efficient and high speed analog-to-digital converters is pushing toward the use of dynamic regenerative comparators to maximize speed and power efficiency. So in this paper, an analysis on the power of the dynamic comparators will be presented with respect to proposed comparator. All these analysis is done Micro wind software.

**Keyword:** - Analog to digital Converter (ADCs), Double Tail Comparator, Voltage swing

### 1. INTRODUCTION

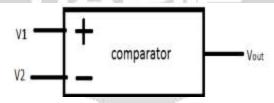

Comparator is one of the fundamental building blocks in most analog to digital converters. Many high speed analog to digital converters such as flash analog to digital converter require high speed and low power comparator with small chip area. In electronics field, a comparator is a device that compares two voltages or currents and outputs a digital signal indicating which is larger. It has two analog input terminals V+and V-and one binary digital output V0. The output is ideally.

$$V0 = 1,$$

if  $V + > V - V0 = 0,$

if  $V + < V - 0.$  (1)

A comparator consists of specialized high-gain differential amplifier. They are commonly used in devices that measure and digitize analog signals, such as analog-to digital converters (ADCs).

Fig-1: Schematic of conventional comparator

Comparator basically compares two voltages or current signals. Figure 1 shows basic operation of comparators where the output is always in digital form, 1 or 0. Apart from technological modifications, developing new circuit structures to avoid stacking of too many transistor between the supply rails is preferable for low voltage operation, without increasing the circuit complexity. Additional circuitry can also be used by adding it to the conventional dynamic comparator to enhance the speed in low supply voltages. Despite this approach, the effect of component mismatch in the additional circuitry on the performance of the comparator should be considered. Here the structure of double-tail dynamic comparator proposed in this research work is based on designing a separate input and cross coupled stage. This separation enables fast operation over a wide common-mode and supply voltage range. A comprehensive analysis on power of dynamic comparators has been presented for various architectures. Here, based on the conventional double-tail structure a new dynamic comparator is presented, which does not require boosted voltage or stacking of too many transistors. Here just by adding a few minimum-size transistors to the conventional

double-tail dynamic comparator, latch delay time is profoundly reduced. This modification also results in considerable power savings when compared to the conventional dynamic comparator and double-tail comparator between two inputs) of a modern rail-to-rail comparator is usually limited only by the full swing of power supply.

# 2. DYNAMIC (CLOCKED REGENARTIVE) COMPARATORS, PROPOSED WORK & SIMULATION RESULT

Clocked regenerative comparators have found wide applications in many high-speed ADCs since they can make fast decisions due to the strong positive feedback. Recently, many analysis have been presented, which investigate the performance of these comparators from different aspects, such as noise, offset and random decision errors, and kick-back noise.

# 2.1 Conventional dynamic comparator

The schematic diagram of the conventional dynamic comparator [1], [2], [13] which is widely used in A/D converters, with high input impedance, rail-to-rail output swing, and no static power consumption. The operation of the comparator is done in two phase which are as follows: First during the reset phase when CLK = 0 and M tail is off, reset transistors (M7–M8) pull both output nodes Out n and Out p to VDD to define a start condition and to have a valid logical level during reset and Second in the comparison phase, when CLK = VDD, transistors M7 and M8 are off, and M tail is on. Output voltages (Out p, Out n), which had been pre-charged to VDD, start to discharge with different discharging rates depending on the corresponding input voltage (INN/INP). Assuming the case where VINP > VINN, Out p discharges faster than Out n, the corresponding p MOS transistor (M5) will turn on initiating the latch regeneration caused by back-to-back inverters (M3, M5 and M4, M6). Thus, Out n pulls to VDD and Out p discharges to ground. If VINP < VINN, the circuits works vice versa.

In principle, this structure has the advantages of high input impedance, rail-to-rail output swing, no static power consumption, and good robustness against noise and mismatch. But the disadvantage on the other hand, is that due to several stacked transistors, the delay time of the latch becomes large due to lower transconductances. Another important drawback of this structure is that there is only one current path, which is not favorable for regeneration.

## 2.2 Double tail comparators

As there are some disadvantages in conventional dynamic comparator so here we are going to study a conventional double-tail comparator [1], [10]. This topology has less stacking and therefore can operate at lower supply voltages. Here the double tail enables both a large current in the latching stage and wider Mtail2, for fast latching independent of the input common-mode voltage (V cm), and a small current in the input stage (small Mtail1), for low offset.

Operation of this comparator as follows:(to and t latch) During reset phase (CLK = 0, Mtail1, and Mtail2 are off), transistors M3-M4 pre-charge fn and fp nodes to VDD, which in turn causes transistors MR1 and MR2 to discharge the output nodes to ground. And then during decision-making phase (CLK = VDD, Mtail1 and Mtail2 turn on), M3-M4 turn off and voltages at nodes fn and fp start to drop with the rate defined by IMtail1/Cfn(p) and on top of this, an input-dependent Differential voltage  $\Delta V fn(p)$  will build up. The intermediate stage formed by MR1 and MR2 passes V fn(p) to the cross coupled inverters and also provides a good shielding between input and output, resulting in reduced value of kickback noise. On the basis of schematic diagram its analog simulation and layout diagram.

#### 2.3 Proposed Comparator

The operation of the proposed comparator is as basic conventional double tail dynamic comparator but the thing is that it has two input controlling transistors Mc1 and Mc2 and two transitional stage transistors MR1 and MR2 as shown in figure 4(a). It too works in Reset and Transition phase has two timing parameters to and t latch On the basis of schematic diagram its analog simulation and layout diagram.

Fig-2: Convolution double tail comparator

Fig-3: Convolution double tail comparator

Fig-4: proposed double tail dynamic comparator.

**Fig-5:** proposed dynamic double tail comparator.

Fig-6: proposed dynamic double tail comparator.

#### 3. CONCLUSIONS

In this paper, we presented a comprehensive delay and power analysis for clocked dynamic comparators is done and for that two common structures of conventional dynamic comparator and conventional double-tail dynamic comparators were studied and analyzed. Also, based on theoretical analyses, a new dynamic comparator with low voltage low-power capability was proposed in order to improve the performance of the comparator.

# 4. REFERENCES

- [1] Samaneh Babayan-Mashhadi and Reza Lofti, "Analysis and Design of a Low-Voltage Low-Power Double-Tail Comparator", in IEEE Transaction on VLSI System Jan. 2013/14.

- [2] B. Goll and H. Zimmermann, "A comparator with reduced delay time in 65-nm CMOS for supply voltages down to 0.65," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 56, no. 11, pp. 810–814, Nov. 2009.

- [3] A. Mesgarani, M. N. Alam, F. Z. Nelson, and S. U. Ay, "Supply boosting technique for designing very low-voltage mixed-signal circuits in standard CMOS," in Proc. IEEE Int. Midwest Symp. Circuits Syst Dig. Tech. Papers, Aug. 2010, pp. 893–896.

- [4] B. Goll and H. Zimmermann, "A 0.12 μm CMOS comparator requiring 0.5V at 600MHz and 1.5V at 6 GHz," in Proc. IEEE Int. Solid-State Circuits Conf., Dig. Tech. Papers, Feb. 2007, pp. 316–317.

- [5] B. Goll and H. Zimmermann, "Low-power 600MHz comparator for 0.5 V supply voltage in 0.12 μm CMOS," IEEE Electron. Lett., vol. 43, no. 7, pp. 388–390, Mar. 2007.

- [6] A. Nikoozadeh and B. Murmann, "An analysis of latched comparator offset due to load capacitor mismatch," IEEE Trans. Circuits Syst.II, Exp. Briefs, vol. 53, no. 12, pp. 1398–1402, Dec. 2006.

- [7] J. He, S. Zhan, D. Chen, and R. J. Geiger, "Analyses of static and dynamic random offset voltages in dynamic comparators," IEEE Trans .Circuits Syst. I, Reg. Papers, vol. 56, no. 5, pp. 911–919, May 2009.

- [8] D. Shinkel, E. Mensink, E. Klumperink, E. van Tuijl, and B. Nauta, "A double-tail latch-type voltage sense amplifier with 18ps Setup+Hold time," in Proc. IEEE Int. Solid-State Circuits Conf., Dig. Tech. Papers, Feb. 2007, pp. 314–315.

- [9] P. M. Figueiredo and J. C. Vital, "Kickback noise reduction technique for CMOS latched comapartors," IEEE Trans. Circuits Syst. II, Exp.Briefs, vol. 53, no. 7, pp. 541–545, Jul. 2006.

- [10] D. Johns and K. Martin, Analog Integrated Circuit Design, New York USA: Wiley, 1997.